大家来找茬——任性的DDR2设计(上)

前面有讲到设计人员因为没有留意到DDR3主控没有读写平衡功能,就按照常规的布线要求来走线,导致数据和时钟信号长度差异较大,最终使得DDR3系统运行不到额定频率。看来没有读写平衡的DDR3,直接按照DDR2的设计规则来做还是比较靠谱的,那么DDR2的设计到底有哪些规则呢?我想大家肯定会比较感兴趣吧。

到底有哪些规则呢?所谓实践出真理,还是先来看看下面的这个案例吧!这个DDR2系统采用8片颗粒表底贴的设计,地址、控制、命令信号一拖八,其余信号一拖二,但最终的系统跑不起来。查看PCB设计,列出部分信号的截图如下,先不评论,各位慢慢开始来找茬吧。

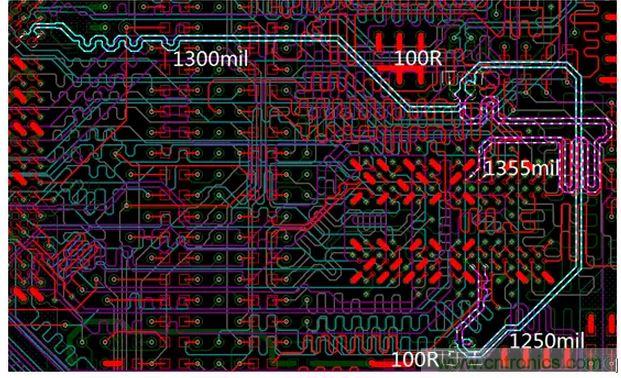

上图高亮部分为时钟信号(绿白)的走线,从主控芯片出来换层经过1300mil到分支过孔,此处端接一个100ohm差分阻抗,再从过孔处分支各走一段1250mil和1350mil的走线到表底两个颗粒,其中一个颗粒再端接一个100欧姆差分电阻,其他的时钟信号也大致如此。

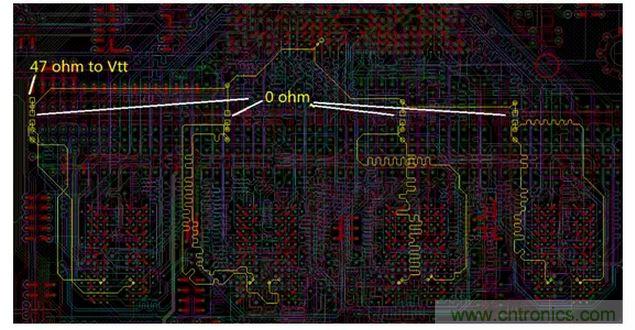

图中黄色高亮部分为地址信号走线,从主控芯片出来马上第一级分支,再约600mil进行第二级分支,再一个分支经过1000mil进行第三级分支,另一分支在50mil左右也开始第三级分支,最后接0ohm串阻约1100mil到颗粒,其中在最边上某一第三分支过孔处上拉一个47ohm电阻到Vtt,其他的地址、控制信号也大致如此结构。

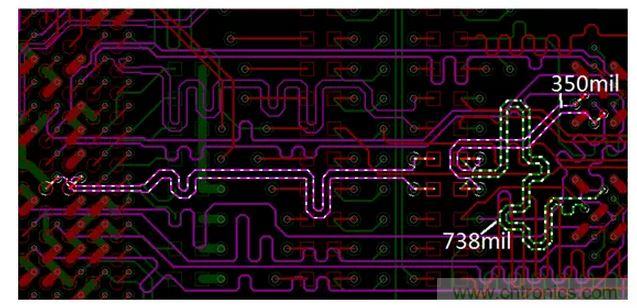

再来看DQS信号,如上图高亮玫红白点信号,进过一级分支各0ohm串阻经350mil和738mil的线路到表底层颗粒,其他的差异不大。

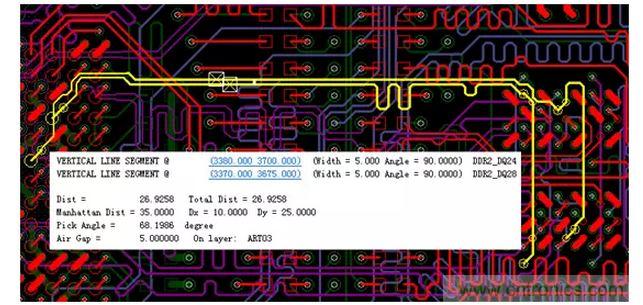

最后再看数据信号,图中黄色高亮部分,采用的菊花链结构,先到其中一个颗粒,再到另一面的第二个颗粒,其他的数据信号也是这种结构。好了,其他的如电源我们就不用看了,看到这里我们已经大致知道这个DDR2系统跑不起来是有原因的啦。