专为USB 3.0端口而设的ESD保护

在为 USB 3.0 系统增加 ESD 保护时,有四个关键技术:低电容/低插入损耗,优化信号完整性,ESD 器件的稳健性及与下游被保护 IC 的相互作用,小型直通(flow-through)ESD 器件封装,优化的布局。只有真正掌握这四个技术,USB 3.0的ESD保护才能滴水不漏。

1. 通用串行总线(USB)保护的发展历程

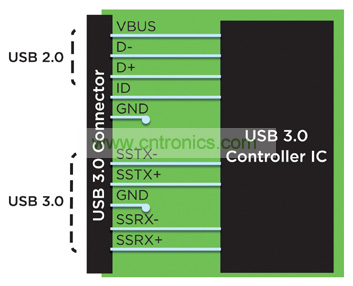

当 USB 2.0 在 1999 年面世时,其 480Mbps 半双工差分信道就对设计人员实现静电放电(electrostatic discharge, ESD)保护带来了艰难的挑战,因为当时的低电容瞬变电压抑制器(Transient Voltage Suppressor, TVS)的寄生电容高达1- 1.2pF。随后推出的 USB 3.0 或超高速(SuperSpeed )USB接口,不但保留了一样的物理 2.0 接口,而且由于增加了两个5Gbps 双单工差分对(一个 Tx 对和一个 Rx 对),保护问题也变得复杂化,如图 1 所示。

过去,分立 TVS 市场落后于摩尔定律(Moore’s Law)。内部的 CPU 时钟频率和内存容量在增加,而外部数字器件 I/O 接口的速度却跟不上。随着 IC 内部的并行 PCI 总线升级到串行总线(PCI Express),外部 I/O 也统一成为高速差分连接,如USB、火线(FireWire)和 eSATA 接口。

图 1:USB 3.0 较 USB 2.0 增加了两个 5Gbps 双单工差分对

保护技术的开发

带宽的迅速增加对连接器构成了另一种保护挑战:芯片组接口速度增加了而硅尺寸却不断减小。这种更快速度和更小型I/O 单元的组合,增加了芯片组 I/O 接口的 ESD 敏感性,同时却限制了外部负载阻抗裕量,因而使得低电容 ESD 保护器的电容不再足够低。因此,设计人员已经从“拷贝和粘贴”通用的分立 ESD 组件布局转变到新设计中,并针对时序、阻抗匹配和插入损耗进行仔细的线路板特性化设计。

USB 3.0 的 ESD 保护

在为 USB 3.0 系统增加 ESD 保护时,设计人员必须考虑所选器件的电容和电感给高速差分信号时序所带来的潜在影响。在每个SuperSpeedUSB差分对中以5Gbps速度工作时,线路上任何的额外阻抗都会使信号失真,导致:

• 更难满足眼图对于上升时间和信号电平的要求

• 给线路板设计带来额外的限制

• 导致不同电缆(质量和长度)间的互操作性问题

为了最大限度地减小对这些高速线路的时序影响,并为下游芯片组提供充分的保护,在选择 ESD 保护器件方面需要考虑。

四个关键技术事项:

1. 低电容/低插入损耗,优化信号完整性

2. ESD 器件的稳健性及与下游被保护 IC 的相互作用

3. 小型直通(flow-through)ESD 器件封装

4. 优化的布局