安森美电路保护方案大观:明白显示ESD有效性和信号完整性

中心议题:

- 当今的集成电路的外部保护要求

- 评估ESD保护的有效性

- PicoGuard® X S技术、硅技术与无源技术比较

- 维持信号完整性、电磁干扰与浪涌保护

随着SoC特征尺寸的减小,器件更易遭受ESD损伤,越来越多纤薄型工业设计更注重小外形封装中的ESD及EMI性能。且保护器件必须完全“透明”,不能降低信号完整性,安森美采用先进技术的电路保护方案让我们知道:ESD有效性和信号完整性可以得到评估和证明。

静电放电(ESD)保护及电磁干扰(EMI)正在成为所有电气设备越来越重要的考虑因素。消费者要求的更多功能特性及纤薄型工业设计要求更加注重小外形封装之中的ESD及EMI性能。

外部保护要求

业界正在采用最先进的技术制造先进的系统级芯片(SoC)。设计人员为了优化功能及芯片尺寸,正在持续不断地减小其芯片设计的最小特征尺寸。但相应的代价是什么?就是特征尺寸的减小,导致器件更易于遭受ESD损伤。

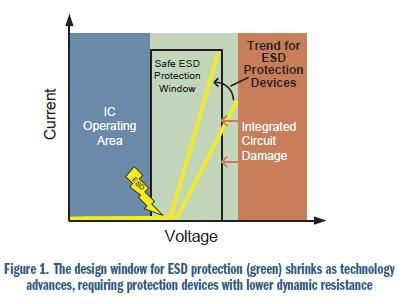

当今的集成电路(IC)给保护功能所留下的设计窗口已经减小。如图1所示,IC有预期的电压及电流工作区域,环绕此区域的是安全过压区。ESD保护必须在安全过压及过流区工作。随着业界趋向以更小几何尺寸和更低电压制造更先进IC,IC的安全工作区也在缩小。

在以前的IC中,设计人员足以选择可在IEC61000-4-2ESD规范规定的ESD冲击下轻易存续的保护产品。因此,大多数保护产品规格书仅列出额定存续等级(如保护器件可在IEC61000-4-2 8 kV 4级接触式放电条件下存续)。但这并未显示保护器件在保护敏感电路时的有效程度。有效ESD保护的关键是限制ESD事件期间的电压,令其处于给定芯片组的安全电压窗口内。ESD保护产品实现有效ESD保护的方式,是在ESD事件期间提供接地的低阻抗电流路径,如图1所示;用于新集成电路的保护产品需要更低的动态阻抗(Rdyn),从而避免可能导致损伤的电压。由于给保护功能所留的设计窗口减小,选择具有低动态阻抗的ESD保护产品变得更加重要,以此确保钳位电压不超过新芯片组的安全保护窗口。因此,ESD保护产品供应商必须提供保护产品有效性的信息,而非仅是保护产品自身的存续等级。

评估ESD保护的有效性

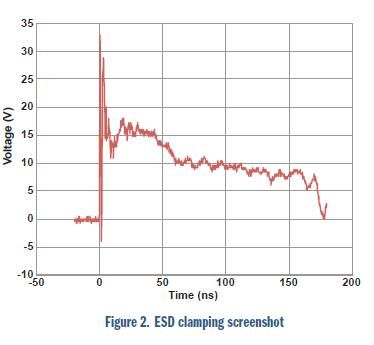

安森美半导体使用两种方法来显示ESD保护的有效性:ESD屏幕截图及传输线路脉冲(TLP)测量。ESD屏幕截图方法捕获保护产品在被施加IEC 61000-4-2 ESD应力(通常为8 kV接触放电)时的电压。图2中所示的屏幕截图显示了安森美半导体的保护器件在遭受8 kV应力条件下在10纳秒(ns)时间内将电压钳位至20 V以下。屏幕截图提供形象直观的保护产品有效性视图,特别适合于比较针对相同应用的两款产品。安森美半导体的应用注释AND8307/D简述了屏幕捕获数据。但屏幕截图并不支持解析出描述保护产品性能的基础参数。TLP方法则提供更加量化的ESD保护器件有效性衡量手段。

下页内容:PicoGuard® X S技术、硅技术与无源技术比较