了解 MOSFET 通态漏源电阻

【导读】分立 MOSFET 数据表中重要的规格之一是漏源通态电阻,缩写为 R DS (on)。这个 R DS (on)想法看起来非常简单:当 FET 处于截止状态时,源极和漏极之间的电阻非常高,以至于我们假设电流为零。当 FET 的栅源电压 (V GS ) 超过阈值电压 (V TH ) 时,它处于“导通状态”,漏极和源极通过电阻等于 R DS(on) 的沟道连接。然而,如果您熟悉 MOSFET 的实际电气行为,您应该很容易认识到该模型与事实不符。

分立 MOSFET 数据表中重要的规格之一是漏源通态电阻,缩写为 R DS (on)。这个 R DS (on)想法看起来非常简单:当 FET 处于截止状态时,源极和漏极之间的电阻非常高,以至于我们假设电流为零。当 FET 的栅源电压 (V GS ) 超过阈值电压 (V TH ) 时,它处于“导通状态”,漏极和源极通过电阻等于 R DS(on) 的沟道连接。然而,如果您熟悉 MOSFET 的实际电气行为,您应该很容易认识到该模型与事实不符。

首先,FET 并不真正具有“导通状态”。当未处于截止状态时(我们在此忽略亚阈值传导),FET 可能处于三极管区域或饱和区域。每个区域都有自己的电流-电压关系。然而,我们可以安全地假设“导通状态”对应于三极管区域,因为 R DS(on)与开关电路相关,而不是小信号放大器和开关电路——例如,用于驱动电机或控制继电器——使用截止区域和三极管区域。

但是,三极管区域不仅受电阻控制,而且受一个相当复杂的方程控制:

_D=mu_nC_{ox}frac{W}{L}left(left(V_{GS}-V_{TH} ight)V_{DS}-frac{1}{2}V_{DS}^2右)

(这是针对 NMOS 器件;PMOS 器件将具有 μ p而不是 μ n。)但是,如果我们忽略 V DS 2项,则方程可以简化如下:

I D = μ n C o x W L( V G S – V T H ) V D S

现在我们确实在漏源电流 (I D ) 和漏源电压 (V DS ) 之间存在线性(即电阻)关系。然而,“电阻”并不是恒定的,就像单纯的电阻器一样;相反,电阻对应于

1μnCoxWL _ _ _ _ _ _ _( VGS - VTH ) _ _ _ _

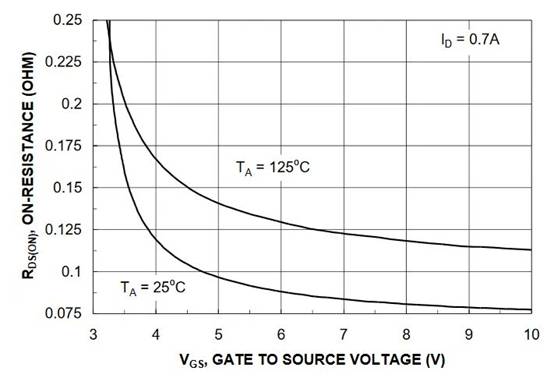

这给我们带来了关于 R DS (on)的重要一点:它受到栅源电压的影响。以下是取自Fairchild NDS351AN MOSFET数据表的示例:

该部件的典型阈值电压为 2.1 V。如果您快速查看 V TH规格和 R DS(on)规格,您可能会认为可以使用 3.3 V 逻辑信号驱动该 FET,并且实现所宣传的导通状态电阻性能。考虑到数据表明确指定了与 R DS(on)规格相对应的栅源电压,这有点粗心;然而,一两个 R DS(on) /V GS数据点并不能体现通态电阻的极端增加,这种情况适用于实际上远高于典型 V TH的栅源电压。因此,这个故事的寓意是 1) 请记住,导通状态(即三极管区域)电阻取决于 V GS,2) 有关详细信息,请参阅 R DS(on)与 V GS的关系图。

此外,导通状态电阻不等于上面给出的三极管区域方程所表示的电阻。后者是 MOSFET 沟道的电阻,而导通电阻包含其他电阻源——键合线、外延层等。电阻特性受制造技术以及 R DS 不同组件各自贡献的影响( on)根据特定设备的预期电压范围而变化。

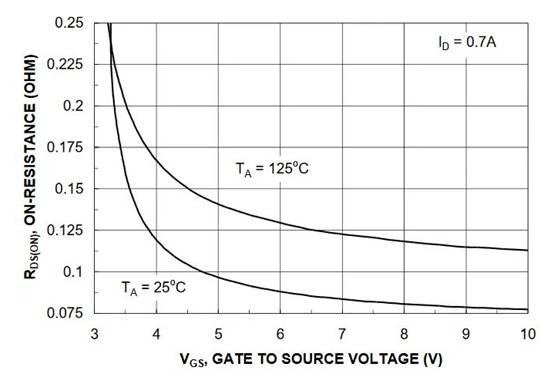

影响通态电阻的另外两个因素是结温和漏极电流,如 NDS351AN 数据表中的这两张图所示:

因此,您可能需要货比三家,花一些时间阅读一些数据表,然后才能找到适合特定开关应用的 MOSFET。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

中国电子智能制造工厂示范线首次亮相第102届中国电子展

ST:不止于“芯”,半导体业如何为ESG可持续发展赋能

如何克服快速、高效的电动汽车充电基础设施的设计挑战

高通公司中国区董事长孟樸:在边缘侧赋能下一轮数字化转型浪潮

数字电源解决方案提供性能和集成增强