英特尔坚持半导体底层技术创新的基础逻辑

2022年7月,中国计算机学会召开了首届芯片大会,以“构建芯生态、链接芯未来”为主题,邀请了海内外学者、研究人员和企业,共同探讨芯片的发展趋势。

大会主席、中国工程院院士孙凝晖在致辞中表示,希望大会能成为产学研交流的平台,并搭建起“四个桥梁”,即计算机相关学科交叉融合的桥梁、计算机学科和集成电路学科的桥梁、芯片学术界和产业界的桥梁、中国芯片和海外芯片交流的桥梁。

英特尔研究院副总裁、英特尔中国研究院院长宋继强博士出席大会,并发表了题为“坚持半导体底层技术创新,激发算力千倍级提升”的主题演讲。一方面分享了英特尔关于数字经济的洞察,另外则是介绍了英特尔在延续摩尔定律方面所取得的技术进展。

英特尔研究院副总裁、英特尔中国研究院院长宋继强博士

为什么要坚持底层创新

目前,中国的数字化转型进程在部分领域已经位于世界前列,甚至已经开始涉及到传统行业。而数字经济增长依赖底层基础设施的支持,包括计算能力、计算效率等,都对数字化和智能化发展带来更好的促进。

宋继强指出:“数字经济的基础设施本质上是一套算力网络,包括如何更好地分配算力、如何根据应用进行调度,如何满足时延、算量和并发数,如何灵活应对不同的数据类型等等。”

而为了将计算与网络更好的融合,我国目前正在稳步推进“东数西算”工程,正是一个以能源、计算能效性为优先综合布局的新型算力网。

“数字化转型真正达到较好效果的前提,需要数据从采集到预处理、分析,再到决策、交付的全生命周期运维。因此未来数据肯定会继续呈现指数型增长。”宋继强断言道。

正如宋继强所述,一方面,数据量会保持指数级增长,另一方面,数据形态也会越来越多元化,对计算的实时性和智能化处理能力的要求也越来越高。从数据量和质来看,传统的单一计算架构肯定会遇到性能和功耗的瓶颈。也正是因此,英特尔才提出了坚持底层创新的观点。

英特尔的底层创新有哪些

宋继强认为,英特尔围绕的底层创新包括两部分,一个突破算力瓶颈,从而应对多样化的数据需求。第二,则是围绕绿色计算,以更低功耗,更节能的方式优化数据的处理。

“异构计算和异构集成是解决问题的新方法。”宋继强解释道,“其中异构计算就是用不同的架构处理不同类型的数据,真正做到“用好的工具解决好的问题”。异构集成则是通过不同工艺下优化好的模块进行集成,从而实现更优化的芯片组合,以高效应对复杂计算。”

在这一大前提下,英特尔首先的工作是在硬件的架构布局上全面发展,提供包括CPU、GPU、IPU、FPGA、AI加速器在内的多种处理器。

另外,更重要的是英特尔的oneAPI软件框架,通过软硬件结合,助力实现更加轻松的异构计算体系。“oneAPI的目的是用户在编写软件过程中,只需指定其实现的功能,而不必明确指定哪些在CPU上运行,哪些在GPU运行,从而可以更加轻松的实现异构计算。这样做的好处是,即便硬件部分升级,实现过程也发生变化,但上层开发代码无需更改,从而实现了更高的开发效率。

“软件框架必须具有开放性,这样才能同时适配未来和现在不断涌现的新兴硬件种类。”

因此,oneAPI的框架划分了几层,底层是硬件的抽象层,定义了硬件的统一描述方法,之上是底层高性能库,针对不同计算内核进行优化。在开发语言方面,支持包括DPC++、SYCL等并行编程。这两层是oneAPI的主要工作,通过硬件描述和优化,以及编程语言,实现了异构计算的底层支持。之后更上层的中间件以及应用和服务,则是直接面对着更多的开发者。

盘点英特尔的底层创新

宋继强盘点了一些英特尔针对底层创新的实践与未来规划,我们也可以看出英特尔对于底层创新的坚持。

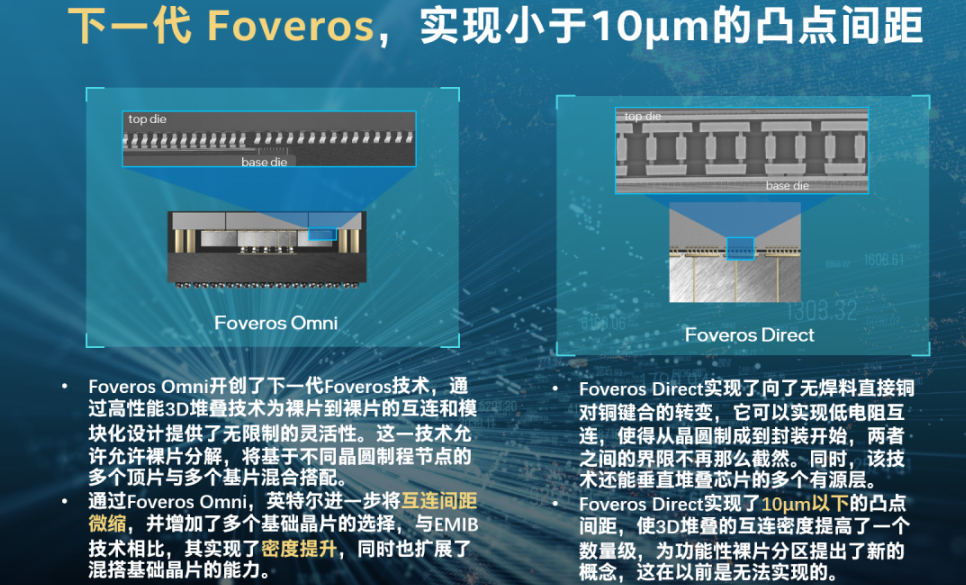

首先对于异构集成,不得不提到的是2.5D封装的EMIB,以及3D的Foveros封装。Foveros可以把不同计算的芯粒(Chiplet)在垂直层面上进行封装。目前,通过更高级的封装微缩技术,封装凸点的间距已经降到了36微米,未来还可进一步降低至10微米以下。Foveros可以保证更高的连线密度,同时其总线传输速率也接近单芯片的速率。

Foveros具体而言分成两种技术,一种被称为Omni,是典型的3D封装,上层是大芯片,底层是小芯片,芯片之间互连的接触点间距微缩至25微米,和EMIB相比密度提升接近4倍。

Direct技术则是更加高级,连接直接采用铜键合技术,无需焊料,因此可实现更低的电阻,并进一步缩小凸点间距,并进一步提升封装密度。

目前英特尔最复杂的SoC——Ponte Vecchio,该SoC包含5个不同制程节点的47种芯片,在水平层面上用EMIB技术封装,在垂直方向上用Foveros,内部包括了至强处理器和Ponte Vecchio GPU,目前可公开的消息是将用于阿贡实验室的极光超级计算机项目。

除了异构集成,英特尔还规划了诸多方向,以应对缩微带来的挑战。首先,是英特尔宣布采用基于高数值孔径的极紫外光刻机(EUV),进一步降低制程工艺的复杂度,并提高良率。

其次,在Intel 20A节点时,将会采用RibbonFET晶体管结构,这种全环绕栅极结构可进一步降低晶体管面积,并提供更快的速度和更强的电流。

同样在Intel 20A节点,英特尔也将采用PowerVia技术,通过底部供电方式,将供电层和逻辑层完全分离,能有效的使用金属层,减少了对二者的权衡,并提升了性能。

如何应对未来

宋继强还介绍了英特尔在2021年IEDM上发表的一些关于基础组件研究的相关学术论文,以应对未来芯片集成的挑战。英特尔将这8篇论文论文分成了三大方向:至关重要的微缩技术,为硅注入新功能以及物理学新概念。

详情请参考:摩尔定律生死讨论的本质是创新大讨论(下篇)

http://news.eeworld.com.cn/manufacture/ic567826.html

此外,宋继强还介绍了英特尔在神经拟态网络计算方面的突破。同CPU或GPU等矩阵运算加速器不同,神经拟态计算无论是在算法层级还是硬件结构设计层级上都实现了突破,不再依靠堆乘加器的方式提供算力,而是模拟人类神经元的结构,利用存算一体化,再通过脉冲神经网络的方式编程,实现人工智能计算。神经拟态网络可以比CPU或GPU降低一千倍以上的功耗,这无疑将是改变计算方式的一个重要途径。

英特尔的Loihi 2,就是这一代表性的实验芯片。Loihi 2采用Intel 4制程,相比上一代产品速度比提升了10倍,神经元数量提升了8倍至百万个,并且面积缩小了一半。此外,为了配合神经拟态计算的开发,英特尔提出了一套完整的开源Lava软件框架。目前Lava在全球有近200家合作伙伴,中国国内就包括了北大、复旦、鹏城实验室、中科院自动化所、联想等。

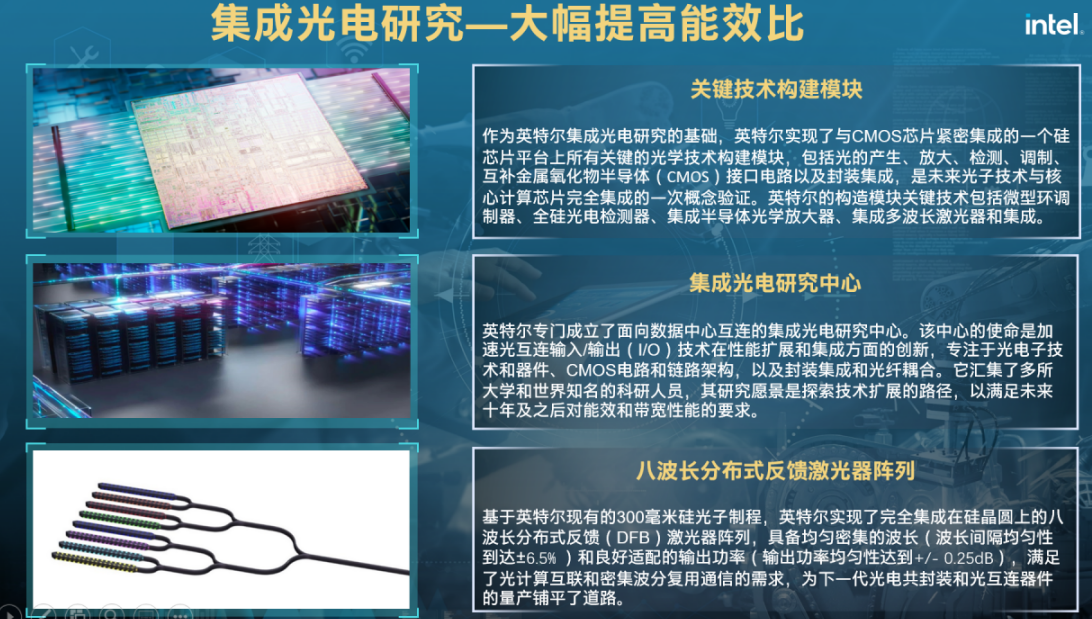

在硅光集成方面,英特尔平台现已实现完整的关键模块集成,包括光电的发射、放大、检测、调制,都可以在标准CMOS工艺下完成,这就意味着未来在短距离传输时,光互连可以具有一定的商业价值。目前英特尔已经成功在8英寸晶圆上开发8个波长的激光器阵列,这也是光互连的关键器件。

摩尔定律的延续

尽管目前关于摩尔定律是否可以延续的探讨屡见不鲜,但我们应该看到,未来随着数字化转型的不断深入,依然需要以计算为基础的底层支撑。而且从英特尔的洞见和趋势,我们也可以看出摩尔定律的演进过程,已不单单仅仅依赖制程,而是通过全方位的推进,以及软硬件的合作,才能真正促进半导体的底层创新。

正如宋继强所说,未来,英特尔将继续携手产学研界各合作伙伴,推动绿色半导体创新,实现千倍级算力提升,并且对地球生态的可持续发展做出贡献。