集成电路3D封装技术的发展史

基于芯片集成度、功能和性能要求,主流晶圆技术节点已降低至28-16nm,甚至已跨入10-7nm制程阶段。然而随着晶圆技术节点不断逼近原子级别,实现等比例缩减的代价变得非常高,摩尔定律即将失效的声音层出不穷。

如何通过封装技术的发展创新来延续摩尔定律,满足未来通信芯片及消费性电子的需求已成为新的热点。目前业界的前沿封装技术包括以晶圆级封装(WLCSP)和载板级封装(PLP)为代表的2.1D封装,以硅转接板和硅桥为代表的2.5D封装,以及基于三维硅通孔(3DTSV)工艺在Z方向上堆叠芯片的3D封装。其中,3D封装在集成度、性能、功耗等方面更具优势,同时设计自由度更高,开发时间更短,是各封装技术中最具发展前景的一种。

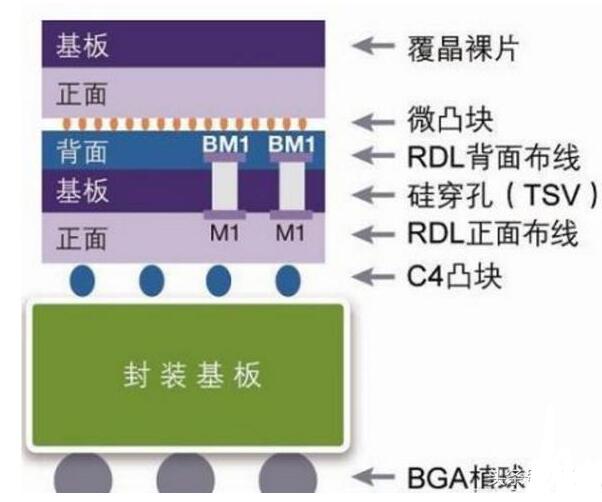

传统意义上3D封装包括2.5D和3DTSV封装技术。硅通孔技术(TSV)实现Die与Die间的垂直互连,通过在Si上打通孔进行芯片间的互连,无需引线键合,有效缩短互连线长度,减少信号传输延迟和损失,提高信号速度和带宽,降低功耗和封装体积,是实现多功能、高性能、高可靠性且更轻、更薄、更小的芯片系统级封装。3DTSV封装结构示意见。

由于3DTSV封装工艺在设计、量产、测试及供应链等方面还不成熟,且工艺成本较高,目前业界采用介于2D和3D之前的2.5D连接层封装形式,通过在Die和基板间添加一层连接层,大幅度提高封装的输入输出(I/O)信号密度,是3DTSV封装大规模商用之前既经济又实用的方案。

2013年以前,2.5DTSV封装技术主要应用于逻辑模块间集成,FPGA芯片等产品的封装,集成度较低。到2014年业界的3DTSV封装技术己有部分应用于内存的芯片封装,用于大容量内存芯片堆叠,同时应用于高性能芯片的高端消费产品中。2015年,2.5DTSV技术开始应用于一些高端的图形处理器(GPU)/中央处理器(CPU)以及网络芯片中,同时“应用处理器(AP)+内存”的集成芯片也开始有部分采用2.5DTSV封装,业界在连接层的成本控制和加工能力方面有一定提高。预计2017/2018年业界在3D封装技术上将取得长足进展,高端手机芯片、大规模I/O的芯片以及高性能芯片中将实现3DTSV封装,同时目前3D封装成本较高的因素也会解决,有望逐步实现大规模量产。