理解低压差稳压器实现系统优化设计

品慧电子讯低压差稳压器(LDO)看似简单,但可提供重要功能,例如将负载与不干净的电源隔离开来或者构建低噪声电源来为敏感电路供电。

本简短教程介绍了一些常用的LDO 相关术语,以及一些基本概念,如压差、裕量电压、静态电流、接地电流、关断电流、效率、直流输入电压和负载调整率、输入电压和负载瞬态响应、电源抑制比(PSRR)、输出噪声和精度。同时,为了方便理解,文中采用了示例和插图。

设计过程中通常到后期才会进行LDO 选型,并且很少进行分析。本文所述的概念将使设计人员能够根据系统要求挑选最佳的LDO。

压差

压差(VDROPOUT)是指输入电压进一步下降而造成LDO 不再能进行调节时的输入至输出电压差。在压差区域内,调整元件作用类似于电阻,阻值等于漏极至源极导通电阻(RDSON)。压差用RDSON和负载电流表示为:

VDROPOUT = ILOAD × RDSON

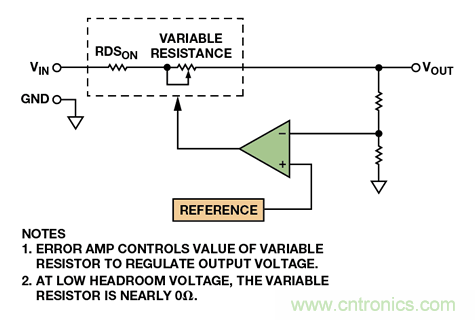

RDSON包括调整元件电阻、片内互连电阻、引脚电阻和线焊电阻,并可通过LDO 的压差进行估算。例如,采用WLCSP 封装时,ADP151在200 mA负载下的最差情况压差为200 mW,因此RDSON约为1.0 Ω。图1 所示为LDO 的原理示意图。在压差模式下,可变电阻接近于零。LDO 无法调节输出电压,因此输入电压和负载调整率、精度、PSRR 和噪声等其他参数都没有意义。

图1. LDO 的原理示意图

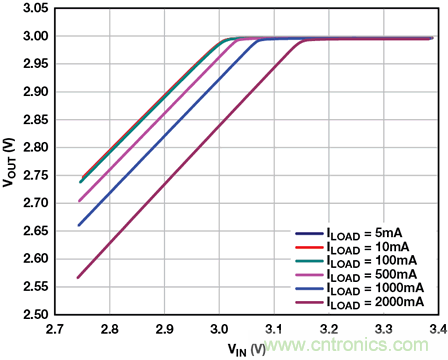

图2 显示了3.0 VADM7172LDO的输出电压与输入电压之间的关系。2 A 时的压差通常为172 mW,因此RDSON约为86 mΩ。压差区域从约3.172 V 的输入电压下降到2.3 V。低于2.3 V 时,该器件不能正常工作。负载电流越小,压差也会按比例下降:在1 A时,压差为86 mV。低压差可最大程度地提高调节器的效率。

图2. 3.0 V ADM7172 LDO的压差区

裕量电压

裕量电压是指LDO 满足其规格所需的输入至输出电压差。数据手 册通常将裕量电压作为指定其他参数时所用的条件。裕量电压通常约为400 mV 至500 mV,但有些LDO 需要高达1.5 V 的裕量电压。裕量电压不应与压差混淆,因为只有当LDO 在压差模式下工作时这两者才相同。

静态电流和接地电流

静态电流(IQ)是指当外部负载电流为零时为LDO 的内部电路供电所需的电流。它包括带隙基准电压源、误差放大器、输出分压器以及过流和过温检测等电路的工作电流。静态电流由拓扑结构、输入电压和温度确定。

IQ = IIN(空载时)

当输入电压在2 V 和5.5 V 之间变化时,ADP160 LDO 的静态电流几乎恒定不变,如图3 所示。

图3. ADP160 LDO的静态电流与输入电压之间的关系

接地电流(IGND)是指输入电流与输出电流之差,并且必然包括静态电流。低接地电流可最大程度地提高LDO 效率。

IGND= IIN– IOUT

图4 显示了ADP160 LDO 的接地电流变化与负载电流之间的关系。

图4. ADP160 LDO接地电流与负载电流之间的关系

对于高性能CMOS LDO,接地电流通常远小于负载电流的1%。接地电流随负载电流的增加而增加,因为PMOS 调整元件的栅极驱动必须增加,以补偿因其RON 引起的压降。在压差区域内,在驱动器级开始饱和时,接地电流也会增加。对于要求具有低功耗或小偏置电流的应用而言,CMOS LDO 至关重要。

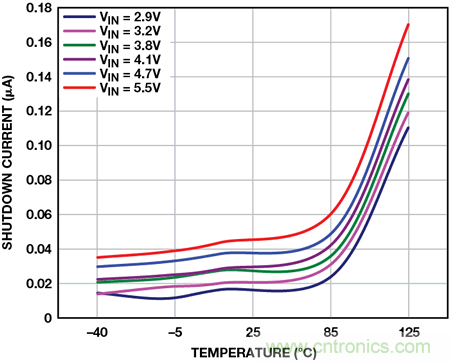

关断电流

关断电流是指输出禁用时LDO 消耗的输入电流。参考电路和误差放大器在关断模式下都不上电。较高的漏电流会导致关断电流随温度升高而增加,如图5 所示。

图5. ADP160 LDO关断电流与温度之间的关系

效率

LDO 的效率由接地电流和输入/输出电压确定:

效率 = IOUT/(IOUT + IGND) × VOUT/VIN × 100%

若需获得较高的效率,必须最大程度地降低裕量电压和接地电流。此外,还必须最大程度地缩小输入和输出之间的电压差。输入至输出电压差是确定效率的内在因素,与负载条件无关。例如,采用5 V 电源供电时,3.3 V LDO 的效率从不会超过66%,但当输入电压降至3.6 V 时,其效率将增加到最高91.7%。LDO 的功耗为(VIN – VOUT) × IOUT.

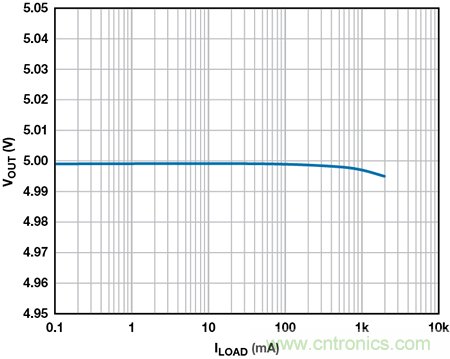

直流负载调整率

负载调整率衡量LDO 在负载条件变化时仍保持额定输出电压的能力。负载调整率定义如下(如图6 所示):

负载调整率 = ?VOUT/?IOUT

图6. ADM7172 LDO输出电压和负载电流之间的关系

直流输入电压调整率

输入电压调整率是衡量LDO 在输入电压变化时仍保持规定输出 电压的能力。输入电压调整率定义为:

输入电压调整率 = ?VOUT/?VIN

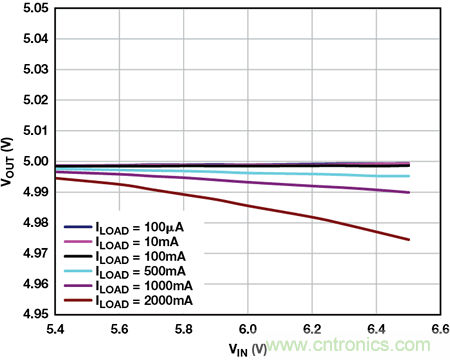

图7 显示了不同负载电流条件下ADM7172的输出电压与输入电压之间的关系图。输入电压调整率随着负载电流增加而变差,原因是LDO 的总环路增益不断降低。此外,LDO 的功耗也随输入至输出电压差增加而增加,这会导致结温升高而使带隙电压和内部失调电压降低。

图7. ADM7172 LDO输出电压和输入电压之间的关系

直流精度

整体精度会考虑输入电压和负载调整率、基准电压漂移和误差放大器电压漂移的影响。稳压电源上的输出电压变化主要是基准电压源和误差放大器的温度变化造成的。如果使用分立电阻来设置输出电压,这些电阻的容差可能是影响整体精度的最主要因素。输入电压和负载调整率与误差放大器失调对整体精度的影响通常为1%至3%。

例如,可利用下列工作特性来计算3.3 V LDO 在0°C 至125°C 温度范围内的总精度:电阻温度系数为±100 ppm/°C,采样电阻容差为±0.25%,因负载调整和输入电压调整而引起的输出电压变化分别为±10 mV 和±5 mV,并且基准电压源的精度为1%。

● 温度导致的误差 = 125°C × ±100 ppm/°C = ±1.25%

● 采样电阻导致的误差 = ±0.25%

● 负载调整率导致的误差 = 100% × (±0.01 V/3.3 V) = ±0.303%

● 输入电压调整率导致的误差 = 100% × (±0.005 V/3.3 V) = ±0.152%

● 基准电压源导致的误差 = ±1%

最差情况误差假定所有误差都沿同一方向变化。

● 最差情况误差 = ±(1.25% + 0.25% + 0.303% + 0.152% + 1%) = ±2.955%

典型误差假定随机变化,因此采用此误差的平方根(rss)。

● 典型误差 = ±√(1.252 + 0.252 + 0.3032 + 0.1522 + 12) = ±1.655%

LDO 从不会超过最差情况误差,而rss 误差是最有可能的误差。误差分布会以rss 误差为中心并扩展到在尾部包括最差情况误差。

负载瞬态响应

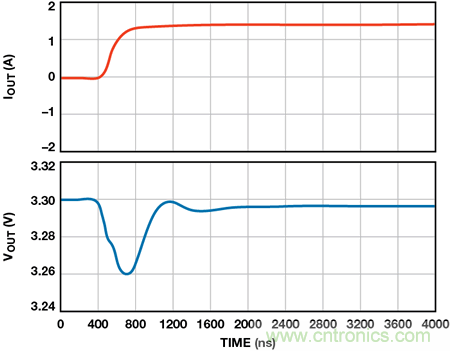

负载瞬态响应是指负载电流阶跃变化时的输出电压变化。它与输出电容值、电容的等效串联电阻(ESR)、LDO 控制环路的增益带宽以及负载电流变化的大小和速率有关。

负载瞬态的变化速率会对负载瞬态响应产生显著影响。如果负载瞬态非常缓慢,比如100 mA/μs,LDO 的控制环路或许能够跟踪该变化。但是,如果负载瞬态较快,环路无法进行补偿,则可能会出现异常行为,例如因低相位裕量而导致过大的振铃。

图8 显示了ADM7172 以3.75 A/μs 的变化速率对1 mA 至1.5 A 负载瞬态的响应曲线。1.5 μs 的0.1%恢复时间和最小振铃表明其具有良好的相位裕量。

图8. ADM7172 负载瞬态响应。400 ns 内产生1 mA 至1.5 A 的负载阶跃(红线)。输出电压(蓝线)

线路瞬态响应

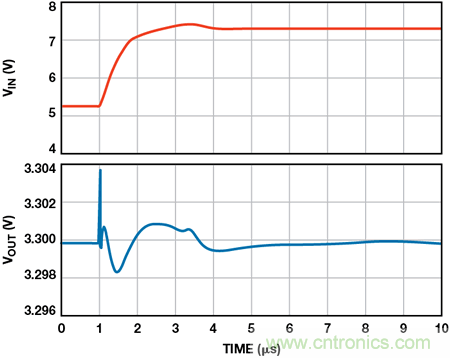

输入电压瞬态响应是指输入电压阶跃变化时的输出电压变化。它与LDO 控制环路的增益带宽以及输入电压变化的大小和速率有关。

图9 显示了ADM7150 对2 V 输入电压阶跃变化的响应。输出电压偏差也显示了环路带宽和PSRR 的特性(参见下一部分)。对应于1.5 μs 内的2 V 变化,输出电压变化约为2 mV,表明约100 kHz时PSRR 约为60 dB。

同样,跟在负载瞬态下一样,输入电压的变化速率也对输入瞬态响应有较大的影响。当输入电压缓慢变化(在LDO 的带宽内只出现一个凹陷)时,可隐藏振铃或其他异常行为。

图9. ADM7150 线路瞬态响应。1.5 μs 内产生5 V 至7 V 的线路阶跃(红线)。输出电压(蓝线)

电源抑制

简单地说,PSRR 衡量电路抑制电源输入端出现的外来信号(噪声和纹波),使这些干扰信号不至于破坏电路输出的性能。PSRR 定义为:

PSRR = 20 × log(VEIN/VEOUT)

其中,VEIN 和VEOUTT 分别是输入端和输出端出现的外来信号。

对于ADC、DAC 和放大器等电路,PSRR 适用于为内部电路供电的输入端。对于LDO,输入电源引脚为内部电路供电的同时也为输出电压供电。PSRR 具有与直流输入电压调整率相同的关系,但包括整个频谱。

100 kHz 至1 MHz 范围内的电源抑制非常重要,因为LDO 经常跟高效的开关电源配合使用来为敏感的模拟电路供电。

LDO 的控制环路往往是确定电源抑制性能的主要因素。同时大容量、低ESR 的电容也对电源抑制性能非常有用,特别是在频率超过控制环路增益带宽的情况下。

PSRR 与频率的关系

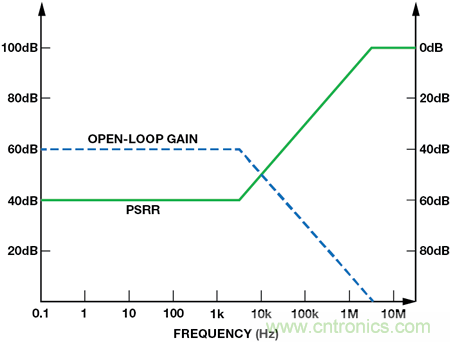

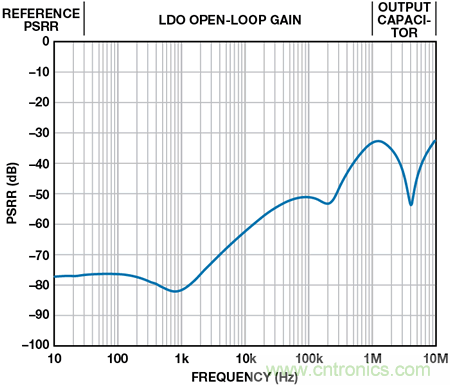

PSRR 不是通过单一值来定义,因为它与频率相关。LDO 由基准电压源、误差放大器,以及MOSFET 或双极性晶体管等功率调整元件组成。误差放大器提供直流增益以便调节输出电压。误差放大器的交流增益特性在很大程度上决定了PSRR。典型LDO 在10 Hz 时可具有高达80 dB 的PSRR,但在数十kHz 时则可降至仅20 dB。

图10 显示了误差放大器的增益带宽和PSRR 之间的关系。这是一个简化的示例,图中忽略了输出电容和调整元件的寄生效应。PSRR 为开环增益的倒数,直到3 kHz 时增益开始下降为止。然后,PSRR 以20 dB/十倍频程的速率降低,直到3 MHz 时达到0 dB。

图10. LDO 增益与PSRR 的简化关系图

图11 显示了用来表征LDO PSRR 的三个主要频域:基准电压PSRR 区、开环增益区和输出电容区。基准电压PSRR 区取决于参考放大器的PSRR 和LDO 的开环增益。理想情况下,参考放大器需与电源扰动完全隔离,但实际上,参考放大器只需抑制最高数十Hz 的电源噪声,因为误差放大器反馈电路能确保在低频时具有高PSRR。

图11. 典型LDO PSRR 与频率的关系

在大约10 Hz 以上的第二区中,PSRR 主要由LDO 的开环增益决定。此区中的PSRR 取决于误差放大器的增益带宽(最高为单位增益频率)。在低频时,误差放大器的交流增益等于直流增益。增益保持不变,直至达到3 dB 截止频率。在高于3 dB 截止频率下,误差放大器的交流增益随着频率增加而降低,速率通常为20 dB/十倍频程。

在误差放大器的单位增益频率以上,控制环路的反馈对PSRR 没有影响,此时PSRR 由输出电容和输入与输出电压之间的任何寄生效应确定。在这些频率下,PSRR 主要受输出电容的ESR,ESL以及电路板布局布线的影响。为了降低任何高频谐振的影响,必须特别注意布局布线。

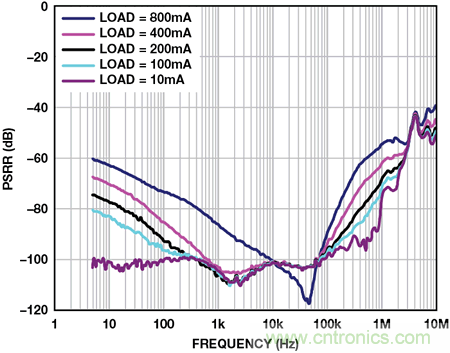

PSRR 与负载电流的关系

负载电流影响误差放大器反馈环路的增益带宽,因此也会影响PSRR。在低负载电流下(通常小于50 mA),调整元件的输出阻抗很高。由于控制环路的负反馈,LDO 的输出近乎是理想的电流源。输出电容和调整元件形成的极点出现在相对较低的频率,因此,PSRR 在低频条件下往往会提高。低电流时输出级的高直流增益往往也会提高误差放大器单位增益点以下各频率的PSRR。

在高负载电流下,LDO 输出不能近似成一个理想电流源。调整元件的输出阻抗会下降,从而导致输出级的增益降低,DC 至反馈环路单位增益频率之间的PSRR 会有所下降。当负载电流增加时,PSRR 会急剧下降,如图12 所示。当负载电流从400 mA 增加到800 mA 时,ADM7150的PSRR 在1 kHz 时降低了20 dB。

输出级带宽随输出极点频率的升高而增加。在高频条件下,PSSR应会随带宽增加而提高,但实际上,由于总环路增益降低,高频PSRR 可能不会提高。一般而言,轻载时的PSRR 优于重载时。

图12. ADM7150 电源抑制与频率的关系(VOUT = 5 V,VIN = 6.2 V)/figcaption>

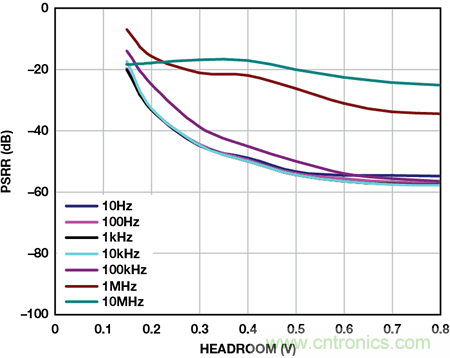

PSRR 与LDO 裕量的关系

PSRR 也与输入到输出电压差(即裕量)有关。对于固定裕量电压,PSRR 随着负载电流的增加而降低;这在高负载电流和小裕量电压时尤其明显。图13 显示了5 V ADM7172 在2 A 负载下PSRR 与裕量电压之间的关系差异。

随着负载电流增加,调整元件(ADM7172 的PMOSFET)脱离饱和状态,进入线性工作区,其增益相应地降低。这导致LDO的总环路增益降低,因而PSRR 下降。裕量电压越小,增益降幅越大。在某些小裕量电压下,控制环路根本没有增益,PSRR 几乎会降至0。

导致环路增益降低的另一个因素是调整元件的非零电阻RDSON。负载电流在RDSON 上引起的任何压降都会导致调整元件有效裕量降低。例如,如果调整元件是一个1 Ω 的器件,当负载电流为200 mA时,裕量将降低200 mV。当LDO 在1 V 或更低的裕量电压下工作时,估算PSRR 时必须考虑此压降。

在压差模式下,PSRR 是由RDSON 和输出电容形成的极点决定的。在非常高的频率下,PSRR 会受输出电容ESR 与RDSON 的比值限制。

图13. ADM7172 电源抑制与裕量的关系(VOUT = 5 V,2 A 负载电流)

比较LDO PSRR 规格

比较LDO 的PSRR 规格时,应确保测量是在相同的测试条件下进行的。许多旧式LDO 仅指定120 Hz 或1 kHz 时的PSRR,而未提及裕量电压或负载电流。至少,电气技术规格表中的PSRR 应针对不同的频率列出。为使比较有意义,最好应使用不同负载和裕量电压下的PSRR 典型工作性能曲线。

输出电容也会影响高频时的LDO PSRR。例如,1 μF 电容的阻抗是10 μF 电容的10 倍。在频率高于误差放大器的单位增益交越频率时,电源噪声的衰减与输出电容有关,此时电容值就特别重要。比较PSRR 数据时,输出电容的类型和值必须相同,否则比较无效。

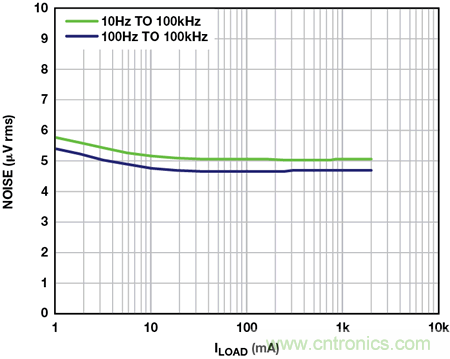

输出噪声电压

输出噪声电压是指在恒定输出电流和无纹波输入电压条件下,给定频率范围(通常为10 Hz 或100 Hz 至100 kHz)上的RMS 输出噪声电压。LDO 的主要输出噪声源是内部基准电压源和误差放大器。现代LDO 采用数十nA 的内部偏置电流工作,以便实现15μA或更低的静态电流。这些低偏置电流要求使用高达GΩ 级的偏置电阻。输出噪声的典型范围为5 μ V r ms 至100 μV rms。图14 显示了ADM7172 输出噪声与负载电流之间的关系。

ADM7172 等部分LDO 可使用外部电阻分压器来设置初始设定点以上的输出电压,使初始设定为1.2 V 的器件可提供3.6 V 输出电压。对于这样的应用,可向该分压器添加降噪网络,以便使输出噪声恢复到接近初始固定电压的水平。

图14. ADM7172 输出噪声与负载电流之间的关系

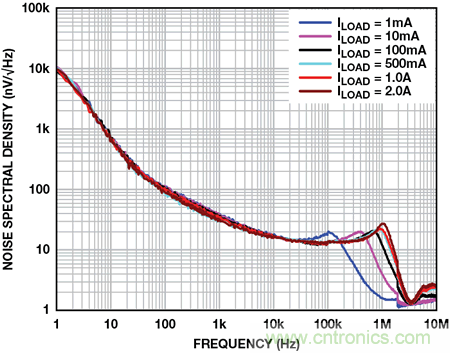

LDO 输出噪声的另一种表示方式是噪声频谱密度。在宽频率范围内绘制给定频率下1 Hz 带宽上的rms 噪声曲线图,然后使用该信息来计算给定频率带宽下的rms 噪声。图15 显示了ADM7172 在1 Hz 到10 MHz 范围内的噪声频谱密度。

图15. ADM7172 噪声频谱密度与负载电流之间的关系

结论

LDO 看似简单实则非常重要。若要正确运用这些LDO 并获得最佳结果,必须综合考虑很多因素。对常用LDO 术语有个基本了解后,设计工程师便可有效运用数据手册来确定对于设计而言最为重要的参数。

推荐阅读:

贴片薄膜电阻和厚膜电阻有什么区别?

如何使用sinc滤波器对∑-?编码数据进行解调?

电路反馈进阶知识:解答的很详细!

基于GP30-F01的超声波水表首波电平选择的幅值分析

这16种PCB焊接缺陷,有哪些危害?