如何优化变压器匝间电容?

品慧电子讯变压器绕组绕在磁芯骨架上,特别是绕组的层数较多时,不可避免的会产生分布电容,由于变压器工作在高频状态下,这些分布电容对变压器的工作状态将产生非常大的影响,如引起波形产生振荡,EMC变差,变压器发热等。所以我们需要优化变压器的匝间电容。

变压器的分布电容主要为4个部分:绕组匝间电容,层间电容,绕组电容和杂散电容。

绕组匝间电容是将变压器两个相邻的绕组比作两块极板,当给两块极板加上适当的电压时,极板之间就会产生电场,并储存电荷。

绕组的层间电容指的是每个单独绕组各层之间的电容。在绕制变压器时,一般会出现单个绕组需要绕2层或2层以上,此时的每2层之间都会形成一个电场,即会产生一个等效电容效应,我们把这个电容称为层间电容。

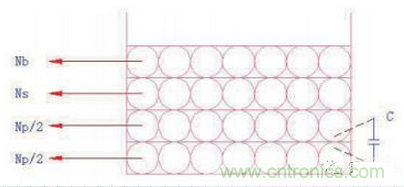

如下图:

电容C就是层间电容

层间电容是变压器的分布电容中对电路影响最重要的因素,因为这个电容会跟漏感在MOS开通与关闭的时候,产生振荡,从而加大MOS与次级Diode的电压应力,使EMC变差。

我们可以用以下四种方法来将它的影响降到可以接受的范围。

方法一:增大绕组的距离来减小层间电容,最有代表性的就是采用三层绝缘线。但这个方法有缺点,因为线的外径粗了之后,带来的后果就是绕线层数的增加,增加了层间电容。

方法二:可通过选择绕线窗口比较宽的磁芯骨架,因为绕线窗口宽,那么单层绕线可以绕更多的匝数,也意味着可以有效的降低绕线层数,层间电容就有效降低了。这是最直接有效的。缺点就是选择磁芯骨架要受到电源结构尺寸的限制。

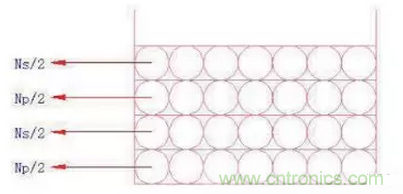

方法三:可以采用交叉堆叠绕法来降低层间电容,如下图

此绕法有显著缺点,会增加初次级之间的耦合面积,也就是会加大初次级绕组之间的电容,使EMC变差。

方法四:改变绕制工艺

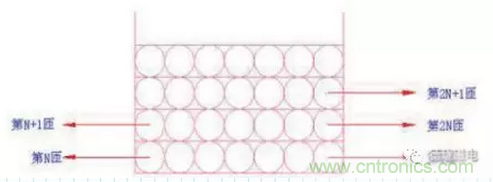

先来看看普通绕法

如上图,这是我们常用的U型绕法,可以看到,在第1匝与第2N匝之间的压差将非常大,由公式Q=C*U可知,压差越大,在这个电容上储存的电荷就越多,这个地方的干扰电压斜率将非常大,在这个地方形成的干扰就越大。

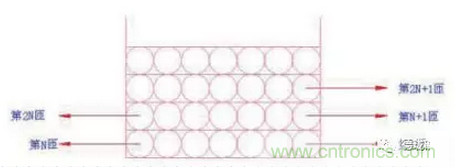

我们可以采用Z型绕法降低这个影响,如下图

此种绕法可以显著降低电压斜率,对EMC是非常有利的。缺点就是绕制工艺相对复杂。

绕组电容就是指绕组之间产生的电容,比如说初级绕组Np与次级绕组Ns之间的电容。由于此电容存在于初次级绕组之间,对电路的EMI是非常不利的,因为初级产生的共模电流信号可以通过这个电容耦合到次级中去,这就造成了非常大的共模干扰,而共模干扰可能会引起电路噪音或者输出不稳定。

办法是在初次级绕组之间加一个屏蔽层,并且用这个屏蔽层接到电路中的某点,来降低电容的影响。这种屏蔽层被称为法拉第屏蔽层,由铜箔或者绕组构成。在用铜箔时,我们一般会绕0.9Ts或者1.1Ts,不会绕1Ts,因为这样容易短路,短路就会导致磁力线短路,电感就接近为零,再反射到初级,初级的电感也为零,这时候如果产品通电的话就会短路炸机了。

变压器的匝间电容是我们不希望产生的,电容越大,对线路的干扰就越大,严重时会改变电路的参数,甚至造成电路无法工作。所以,在设计变压器时,应尽量进行合理的材料选择,优化绕制工艺,以达到减少匝间电容的目的。