句句经典!资深工程师分享关于Flyback电源各层面的分析与总结

品慧电子讯:以下是一位资深工程师分享关于Flyback电源各层面的分析与总结,句句经典!各位工程师千万不要错过......

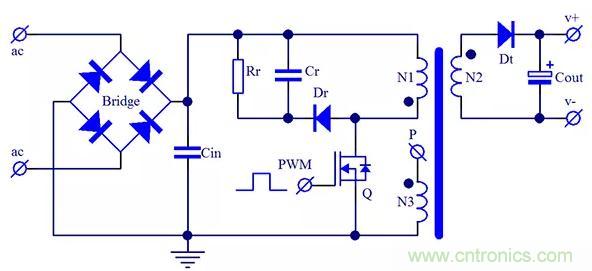

对于Flyback拓扑结构的诠释......

Flyback的五之最

1)应用最多的变换器

生产数量、人均拥有量、总用电容量?

2)性能最差的变换器

能效、电磁兼容性

3)工况最差的变换器

硬开关、电压应力、电流应力、磁利用率、EMC应力

4)任务最重的变换器

安规隔离、宽电压应用、PFC应用,待机

5)最简单的变换器

还有比它更简单的隔离变换器?集成度越来越高、元件越来越少,做出来很容易,做好呢?

什么叫好?

●比别人做的好

●没有比这个更好

●为什么我做的总没别人做的好

●为什么有那么几个人做出来的反激就是明显比别人好

●我手上这个还能不能更好

●如果能证明这个不可能更好,那就是最好

开关电源很多指标:

效率、成本、安全、电磁兼容性、待机、能效、可靠性、稳定性、保护、体积(功率密度)、超薄、精度、纹波、电压调整率、负载调整率、交叉调整率、温度、寿命、功率因数、总谐波。

好不好,看效率:

●效率做起来,才谈得上其他的

●先做好效率,再说其余

●牺牲效率的设计不是好设计

●效率是一点一点抠出来的

●对效率的追求,永远是值得的

●多花点时间优化效率,就是效率

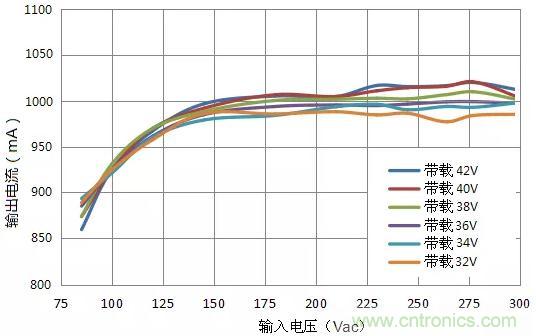

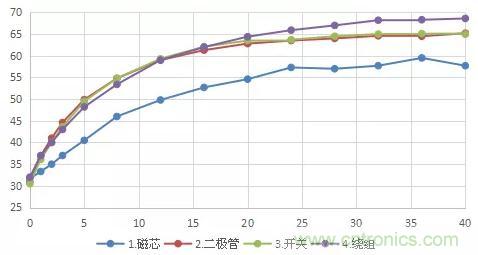

效率能做到多高呢?

●很多人以88%为标准,几年前的标准

●估计现在能批量出货的应该在90%以上,才有竞争力

●有的人轻易就能做到91、92%以上去

●还有个别人,一不小心就做到93%以上去

所谓高手:定一个设计标杆:整机效率94%

●觉得太高?那就93%,不能再低了

●这是一个在特定情况下可以实现的整机效率

●这是一个难以实现的整机效率。

●即使没能实现,我们也应该知道自己的差距

●即使没能实现,我们也应该知道为什么没能实现,是哪些因素导致的

一、什么在影响反激的效率?

1.漏感

●漏感问题是反激变换器的基本问题。漏感是硬伤。要实现高效率,控制漏感是重头戏。先做好漏感,再说其余。

●漏感有多大?意味着能量传递损失多大,变换器效率损失有多大,钳位电路热损耗有多大。这都是额外的,其他变换器没有的。

2.较大的峰值电流 Ipk

●反激的峰值电流较之其他拓扑更大,原因是其储能/释能这种间歇工作模式决定的,占空比较小。

●临界模式、断续模式、PFC控制、宽电压应用更加剧了峰值电流应力。

●峰值电流决定一个反激变压器的磁应力,导致磁利用率较低。

●峰值电流还与开关(以及副边二极管)导通损耗直接相对应。

3.较高的原边电压应力

●反激的原边电压应力较之其他拓扑更大,原因是反射电压、漏感尖峰电压叠加在输入电压上,导致开关电压应力为输入电压的1.5~2倍。

●导致:

a)硬开关动作的损耗剧增(因各种寄生电容导致的损耗增加2~4倍)

b)开关内寄生二极管反向恢复电流激增(导致关断损耗激增)。

c)必须使用耐压高出1.5~2倍的开关,其饱和压降大幅度提高,导通损耗剧增。

4.更高的副边二极管电压应力

●反激的副边二极管电压应力更是增加得离谱,按市电AC/DC变换的典型参数,这个电压应力更是高到了其输出电压的3到5倍,还可能有可观的尖峰电压叠加。

●导致:

a)二极管翻转动作的损耗剧增(因各种寄生电容导致的损耗增加10~30倍)

b)二极管反向恢复电流激增(不要相信此处没有反向恢复的说法)

c)必须使用耐压高出输出电压几倍的二极管,其饱和压降大幅度提高,导通损耗剧增

二、拓扑环境层面的设计考虑

高效率的反激设计应该比一般设计更注意仔细追究拓扑应用环境,这是因为对效率的极限追求也是对其应用环境的极限追求,要让电路工作处于最明确、最舒适、最能扬长避短、最能发挥到极限的环境。

1.选择一个较软的拓扑控制模式。准谐振(QR)模式是首选,而CCM、CRM模式可能效率较低。其他诸如谐振模式、无损钳位模式、Sepic模式等,由于技术尚不成熟一般不予考虑。

2.输出电压较低时,副边考虑同步整流是好主意。

3.尽量考虑采用专用控制芯片、有口碑的芯片、原边控制的芯片。避免使用6562、3842这样的通用芯片去做反激,用一大堆运放达成的控制环路更是不可取。不是因为这些芯片不能用,而是要伺候这些芯片是很难受的。

4.认真论证你的最低输入电压,也就是最大峰值电流 Ipk 的取值。全电压的必要性,过渡模式(CCM模式)的必要性,限流模式(OCP模式)的必要性,控制转折点设置在哪里?任何时候都不要让 Ipk 失控。开机冲击和短路冲击对 Ipk 的影响也要考虑。

5.认真论证你的最高输入电压,市电AC/DC应用按264Vac做显然是有问题的,小区电压飙到264Vac以上是经常的。建议按277Vac(必要时再增加一点余量)考虑。

6.认真论证你的最高输出电压,或者CV/CC模式的最大输出功率。充分考虑各种情况下输出电压意外飙高的可能性,并选择一款OVP嗨得住的芯片。OVP是否嗨得住,不仅涉及最高输出电压带来的最高电压应力、功率应力,还直接关乎假负载的损耗功率。最高输出电压就是脱离OVP保护模式后的第一个电压。

三、电路运行层面的设计考虑

1.输入回路干净利落,避免热敏电阻、保险电阻的设计,硅桥要电流稍大的。共模差模带来的损耗要斤斤计较,一级两级、个大个小、线粗线细之间的差别是很大的。这还涉及EMC设计水平,如何做到用最少的共模差模解决问题?

2.开关的选型,MOS最好是外置的,这样方便选型和控制。内阻(Rdson)尽量小一点,Cool-MOSc也是可以的。最重要的是耐压,市电 AC/DC 典型应用,MOS 耐压首选 650V 的,耐压更低的应该嗨不住,耐压更高的特性急剧恶化,其价格、内阻都是很难接受的。

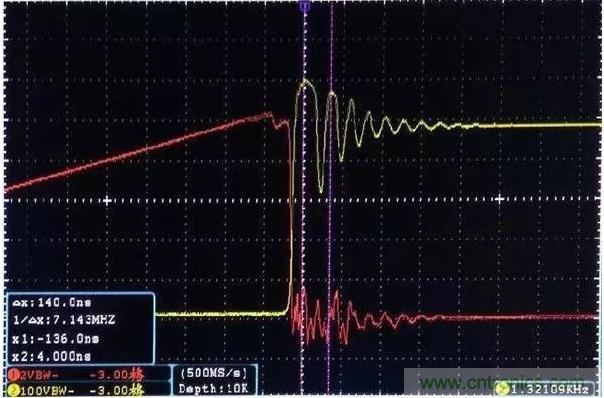

3.驱动能力要足够,Rg下拉、上拉电阻要分开(上拉电阻与二极管并联后串下拉电阻)。关断要干净利落,一定不能让米勒平台出现在 Ipk 位置。

4.在高压端通过电阻实现的电压采样、VCC启动、线电压补偿、安规电容放电等电路是要耗电的。副边假负载、副边采样控制电路也是要耗电的。这些电路要优化,其能耗要追究。

5.最敏感的电流采样、过零(谷底)采样、FB采样电路要精心布置,电路要简洁,阻抗要匹配,杂散参数影响要小,PCB要安静。这是因为高效率电路对这些细微的控制有更高的要求,不能出问题。

6.各部波形要正常,没有奇怪的、离谱的东西。环路、高PFC电路的主要参数要调试好,主要指标 PF 和 THD 要基本达到要求,工作稳定,不能有振荡,在这个前提下做的效率优化才有意义。

7.在最后优化效果出来前,(在经验不足时)某些要影响效率的次要电路可以先裸奔。比如:磁珠要取消、DS上并联的电容要取消、差模共模可短路、钳位功率最小化(降低电压运行看情况)、副边二极管吸收电路不连接(用高耐压二极管先代替看情况)、假负载功率最小化,CS采样电阻最小化(非OCP模式),甚至VCC供电和副边控制电路用电可考虑用电池组临时供电。以免这些电路的设置不合理影响主电路运行工况,造成误判。

四、变压器设计

高效率反激变换器大部分设计技巧隐藏在变压器里,绕组结构和磁决定变压(换)器性能是绕组结构在决定运行参数。

1.绕组结构的约束条件:

●窗口约束

原边副边窗口分配用铜量大致相等,满足几何和能量的大致对应。技巧是分配要合理、线包要基本饱满。

●三明治约束

二夹一的意思,是降低漏感的重要措施,技巧是减少EMC结构、安规结构的不利影响,耦合要紧密。还需注意气隙对绕组的影响、磁芯作为导体的影响,辅助绕组的结构和位置。

●整层约束

是降低漏感最重要的措施,技巧是无论如何都要整层密绕、少半匝都不行,均绕不行、半层更不行,匝数太少就双线或多线并绕、或者用与槽宽等宽的铜箔叠绕。

绕组结构设计可以归结为平面几何问题。设计目标是漏感最小化、气隙最小化,需要较多的经验、技巧、时间、智慧、精力才能达成。是反激变换器设计的重点,也是高效率反激设计的关键所在。漏感的设计标杆:1%,否则不能实现高效率。

2.绕组结构决定运行参数:

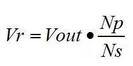

●一个绕组结构最终与原边副边匝数相对应,其匝比决定反射电压 :

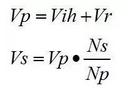

●反射电压决定原边MOS和副边二极管电压应力(不含尖峰部分):

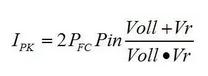

● 有了反射电压即可算出原边电流应力:

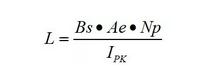

●由此得到原边电感量:

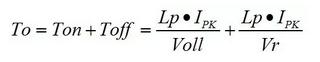

●基于临界模式的最大PWM特征周期:

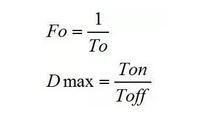

●与之对应的最低特征频率和最大占空比:

3.磁参数优化:

1)磁芯选择

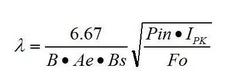

给出一个(PC40材质的)磁功率应力的经验公式:

●可由此大致判断(λ=1)磁芯是否合适。高效率的设计要求磁应力不能太紧张,也就是变压器(包括绕组和磁芯)的发热不要成为整个电源最突出的。当热应力突出时,应增加磁芯的 Ae.B 或者使用更好的材质。

磁芯型号也有影响,骨架槽宽 B 越大于槽深 H 的偏平窗口由于越容易满足整层约束而更有利于减少漏感。

2)磁饱和强度Bs

优化方向是Bs值最优化,约束条件是磁芯品质,可按 Bs(或原边电感量 Lp)扩大20%~30%余量后 Ipk 波形可见临界饱和迹象为判据确定Bs取值。更高的Bs取值,对应更小的气隙、更小的漏感,更小的尖峰电压、可能更高的整机效率。但太高的Bs取值会使上述余量更小、磁芯的品质控制困难、成品率降低。

Bs不能靠估计,要实测。Bs有个最佳值,PC40材质,大约为0.3T,偏离这个最佳值都会降低效率。

4.运行参数优化:

1)匝比 Np/Ns,反射电压 Vr

优化方向是匝比和反射电压最优化,约束条件是原边电压应力(即MOS管耐压)。更大的匝比对应更高的反射电压Vr、更小的峰值电流 Ipk、可能更小的漏感、更大的最大占空比 Dmax、更低的副边电压应力Vs(以便使用最低耐压的肖特基)。但反射电压太高会导致开关电压应力及开关损耗增加,抵消以上效应,应适可而止。

2)原边匝数Np

优化方向是原边匝数最优化,约束条件是磁损和开关损耗。更少的原边匝数,对应更小的气隙、更小的漏感绝对值、更小的尖峰、更小原边电感量 Lp、更高的特征频率 Fo、更低的铜损、更大的磁损、更大的开关损耗、可能更高的输入电压低端效率、可能更低的输入电压高端效率。根据这些表现,优化到佳值。

五、电路优化配合

一个好的变压器设计出来以后,需要电路与之配合,才能充分发挥高效率特性。

1.钳位电路

尖峰一定是有的,尖峰大小取决于漏感,钳位功率也取决于漏感。钳位二极管耐压应不低于MOS管耐压,一般应考虑用快恢复的。避免使用4007、磁珠、二极管上串电阻,这些东西是要发热的。钳位电阻应与钳位电容配合,考虑到漏感能量有一部分消耗在开关上,钳位功率控制在漏感的50%以下为宜。

2.副边二极管反压尖峰 RC 吸收电路

非CCM模式,建议在原边MOS驱动上动手脚,增加导通电阻、减缓导通速率、利用米勒效应转移功率、达成减小甚至完全消除副边二极管反压尖峰之目的。此法可完全省掉RC吸收,收获最高整机效率。即使有过渡到CCM模式,上述导通电阻也应做适应性调整,采用一个合理取值,配合RC吸收达成目的。

RC吸收是有损吸收,对于每一个案例、每一个吸收电容值,都有一个最佳电阻值配合使尖峰最小化,找到这个电阻值,达成最小损耗的吸收。在多路输出时,主要的回路才需要RC吸收(并按上面的方法使损耗最小化),次要的回路建议裸奔(用二极管耐压去扛),或者稍微吸收一下即可,切不可喧宾夺主。

3.副边二极管耐压

在漏感最小化、吸收最佳配合后,副边二极管电压应力已经最小化了,按此电压应力选择一款最低耐压的肖特基,即达成最高效应用。即使有同步整流助力也应如此。此举是提高整机效率最重要的措施之一。

六、其它电路优化配合

1.副边控制电路耗电最小化设计 尽量在 TL431(1~2mA)范围内解决问题,假负载电流、吸收回路电流亦可利用起来为其供电。避免单独绕组供电的设计。

2.辅助绕组电压最小化设计 以芯片VCC工况为准,电压匹配、电流够用即可,VCC电容容量够用即可。能少一匝就少绕一匝的意思,避免为加快启动而故意增加VCC电流的设计。

3.电流采样电阻Rcs 可能成为PCB板上的热点,也就是损耗点。在必须采样时,应该纠结芯片的采样阀值设置,尽量低一点有利效率;否则可适当减小此电阻值,减小热损失。

4.EMC最优化设计 对高效率电源而言,EMC最优化设计的另一个目的是简化端口的差模共模工程,从而减少器件损耗、提高效率。这些措施是:

a、变压器 EMC 结构要追究、隔离屏蔽要做好

b、 PCB 要做好

c、 Y 电容要用两只来湮灭偶极子噪音

d、开关导通速率宜缓不宜急

e、 共模差模结构要合理

5.热平衡设计 仔细考察电源的热景象,主要温升器件的极端最大温升应大致一致,一般可以50C°为限值。温升还可判断变压器设计的合理性、散热工的合理性、意外的温升点意味着高效率设计的败笔。