专家剖析:射频系统中MEMS时钟振荡器如何使劲?

品慧电子讯本文介绍基于MEMS的DCXO和传统牵引振荡器在抖动清除和通信同步锁相环路应用中的比较。并以实例说明如何应用高性能DCXO和FPGA来设计一个简洁的、全数字化的抖动清除锁相环电路。时钟振荡器和射频系统时钟振荡器作为频率合成锁相环的参考信号源,广泛应用于各种射频系统的本地振荡器、时钟发生电路和通信同步电路(见图1)。本地振荡器通过锁相环路倍频,产生射频混频电路所需要的本振驱动信号。参考时钟振荡器的频率准确度和稳定度决定了本振信号和射频收发器工作频率的准确度和稳定度。对频率精度要求不高的射频系统使用射频芯片内置振荡器电路与外接石英晶体谐振器组成参考时钟振荡器,这可以达到10-4~10-5的频率精度。对频率误差和环境稳定性要求更高的射频通信系统需要独立的温补振荡器(TCXO)或频率可以微调的牵引温补振荡器(VC-TCXO)来达到10-6~10-7精度等级。恒温振荡器(OCXO)隔离了外部温度对振荡器的影响,使频率精度达到了10-8~10-9,能满足无线基站和高容量光纤传输网络节点的时间和频率基准要求。

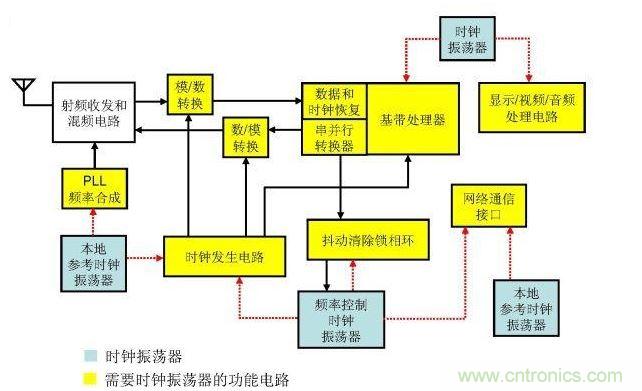

图1:时钟振荡器在射频系统中的应用射频系统的时钟发生电路可提供数模和模数转换电路的取样时钟、基带数字信号处理器时钟、串行数据和时钟恢复电路的本地时钟。作为时钟发生电路的参考源,时钟振荡器的相位噪声和抖动性能,对模数信号转换的信噪比和数据传输误码率和恢复时钟的抖动都有重要影响。射频系统的通信同步和抖动清除电路也是时钟振荡器的重要应用。经过无线或有线信号传输和时钟恢复过程,受信道噪声的影响,系统时钟的相位噪声和抖动会增加。抖动清除电路应用窄带锁相环路和具有低相位噪声特性的牵引振荡器(VCXO)对系统时钟相位噪声进行过滤,可获得低抖动的时钟输出。全硅MEMS时钟振荡器的频率稳定性和相位噪声性能在最近几年取得了突破性的进展。MEMS振荡器也展现了优异的环境稳定性(全温度、冲击、振动、电磁干扰、电源噪声)和器件可靠性。 在架构上,全硅MEMS时钟振荡器结合了固定频率的MEMS谐振器和提供温度补偿和频率合成功能的、具有高分辨率的、分数N锁相环电路。基于这一架构已经开发出各种不同类别的时钟振荡器—从单端和差分信号输出的标准振荡器、TCXO、VC-TCXO、VCXO到数字控制振荡器(DCXO)。本文介绍基于MEMS的DCXO和传统牵引振荡器在抖动清除和通信同步锁相环路应用中的比较。并以实例说明如何应用高性能DCXO和FPGA来设计一个简洁的、全数字化的抖动清除锁相环电路。123下一页>

图1:时钟振荡器在射频系统中的应用射频系统的时钟发生电路可提供数模和模数转换电路的取样时钟、基带数字信号处理器时钟、串行数据和时钟恢复电路的本地时钟。作为时钟发生电路的参考源,时钟振荡器的相位噪声和抖动性能,对模数信号转换的信噪比和数据传输误码率和恢复时钟的抖动都有重要影响。射频系统的通信同步和抖动清除电路也是时钟振荡器的重要应用。经过无线或有线信号传输和时钟恢复过程,受信道噪声的影响,系统时钟的相位噪声和抖动会增加。抖动清除电路应用窄带锁相环路和具有低相位噪声特性的牵引振荡器(VCXO)对系统时钟相位噪声进行过滤,可获得低抖动的时钟输出。全硅MEMS时钟振荡器的频率稳定性和相位噪声性能在最近几年取得了突破性的进展。MEMS振荡器也展现了优异的环境稳定性(全温度、冲击、振动、电磁干扰、电源噪声)和器件可靠性。 在架构上,全硅MEMS时钟振荡器结合了固定频率的MEMS谐振器和提供温度补偿和频率合成功能的、具有高分辨率的、分数N锁相环电路。基于这一架构已经开发出各种不同类别的时钟振荡器—从单端和差分信号输出的标准振荡器、TCXO、VC-TCXO、VCXO到数字控制振荡器(DCXO)。本文介绍基于MEMS的DCXO和传统牵引振荡器在抖动清除和通信同步锁相环路应用中的比较。并以实例说明如何应用高性能DCXO和FPGA来设计一个简洁的、全数字化的抖动清除锁相环电路。123下一页> - 第一页:时钟振荡器和射频系统

- 第二页:频率控制方法及DCXO参数的选择

- 第三页:DCXO抖动清除电路实现

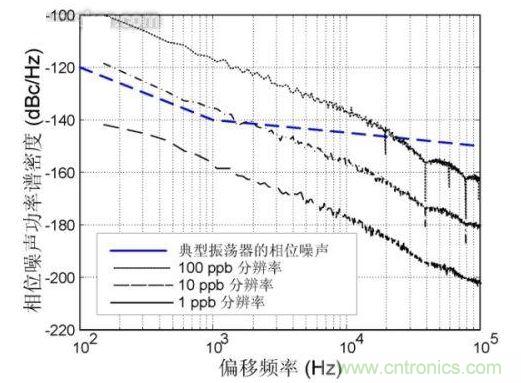

图2:频率分辨率量化引起的相位噪声,DCXO 10 MHz输出,频率更新速率每秒25000次<上一页123下一页>

图2:频率分辨率量化引起的相位噪声,DCXO 10 MHz输出,频率更新速率每秒25000次<上一页123下一页> - 第一页:时钟振荡器和射频系统

- 第二页:频率控制方法及DCXO参数的选择

- 第三页:DCXO抖动清除电路实现

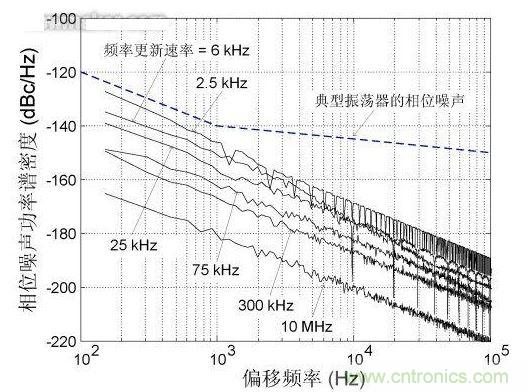

图3:频率更新速率对近载波相位噪声的影响,DCXO频率分辨率1 ppbDCXO抖动清除电路实现应用于抖动清除锁相环路的DCXO应具有足够高的频率更新速率,极高的频率分辨率,低相位噪声性能和适合系统要求的频率牵引范围。图4是一个基于DCXO和FPGA的全数字锁相环路125MHz时钟的抖动清除电路。该设计选择的SiT3907 DCXO可以提供最高每秒25,000次的频率更新速率,1ppb的高频率分辨率,小于1 ps RMS(12kHz~20MHz)的积分相位抖动特性和最高达±1600ppm的线性牵引范围。全数字锁相环电路包括输入时钟分频器,相位累加器、环路滤波器,环路状态控制电路,可选的CIC滤波器,以及驱动DCXO芯片的串行通信接口。

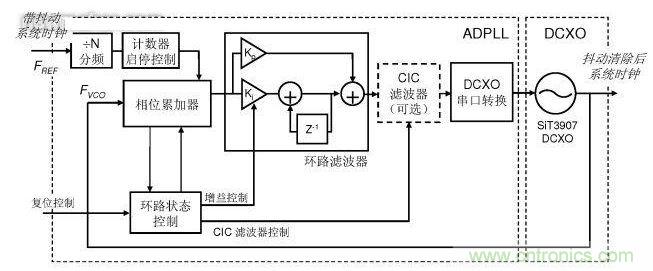

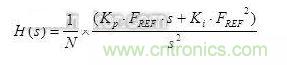

图3:频率更新速率对近载波相位噪声的影响,DCXO频率分辨率1 ppbDCXO抖动清除电路实现应用于抖动清除锁相环路的DCXO应具有足够高的频率更新速率,极高的频率分辨率,低相位噪声性能和适合系统要求的频率牵引范围。图4是一个基于DCXO和FPGA的全数字锁相环路125MHz时钟的抖动清除电路。该设计选择的SiT3907 DCXO可以提供最高每秒25,000次的频率更新速率,1ppb的高频率分辨率,小于1 ps RMS(12kHz~20MHz)的积分相位抖动特性和最高达±1600ppm的线性牵引范围。全数字锁相环电路包括输入时钟分频器,相位累加器、环路滤波器,环路状态控制电路,可选的CIC滤波器,以及驱动DCXO芯片的串行通信接口。 图4:基于DCXO和ADPLL的抖动清除电路框图相位累加器是一个启停计数器,由反馈的DCXO时钟驱动。计数器周期的启动和结束由输入时钟分频脉冲触发。输入时钟预分频值N决定了相位累加器的采样率。环路滤波器需要保持低带宽,一般不大于相位累加器采样率的十分之一。环路状态控制电路在检测到锁定状态之后可降低环路增益,进一步提高噪声抑制能力。图4的数字锁相环电路还包括两个附加功能,可以降低相位噪声和抖动。第一个功能是环路状态控制电路的更新或复位信号,可最小化相位误差的积累。第二个功能是可选的CIC滤波器,可降低开环增益。没有打开CIC滤波器的开环增益H(s)为:

图4:基于DCXO和ADPLL的抖动清除电路框图相位累加器是一个启停计数器,由反馈的DCXO时钟驱动。计数器周期的启动和结束由输入时钟分频脉冲触发。输入时钟预分频值N决定了相位累加器的采样率。环路滤波器需要保持低带宽,一般不大于相位累加器采样率的十分之一。环路状态控制电路在检测到锁定状态之后可降低环路增益,进一步提高噪声抑制能力。图4的数字锁相环电路还包括两个附加功能,可以降低相位噪声和抖动。第一个功能是环路状态控制电路的更新或复位信号,可最小化相位误差的积累。第二个功能是可选的CIC滤波器,可降低开环增益。没有打开CIC滤波器的开环增益H(s)为: 其中,N是系统时钟与相位比较器采样频率之间的比率。当环路滤波器增益在锁定过程中的两个值之间交替时,CIC滤波器可减轻增益变化对输出的影响。另外,调节增益Kp和Ki之间的比例可以增加稳定性、提高性能。

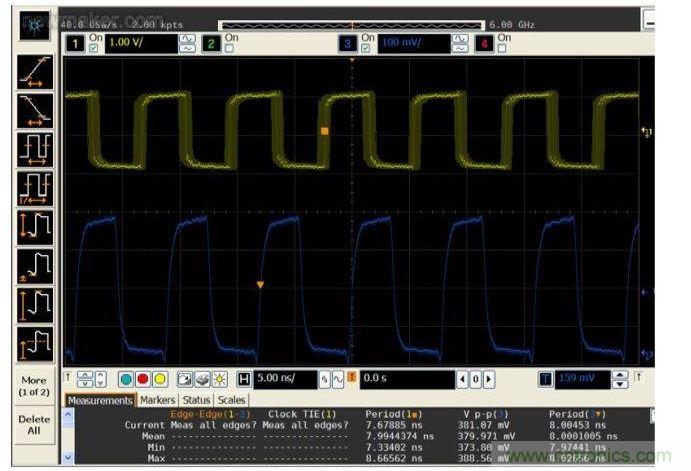

其中,N是系统时钟与相位比较器采样频率之间的比率。当环路滤波器增益在锁定过程中的两个值之间交替时,CIC滤波器可减轻增益变化对输出的影响。另外,调节增益Kp和Ki之间的比例可以增加稳定性、提高性能。 图5:比较带抖动的125 MHz系统时钟输入(黄色,顶部)与抖动清除后的输出时钟(蓝色,底部)实验测量该设计的相位噪声、相位抖动和抖动衰减的有效性。测量数据显示对正弦信号调制抖动的衰减可高达60dB,并导致综合相位抖动显著降低。图5显示抖动清除电路对时钟信号的影响;从一个能观察到明显抖动的125MHz系统时钟开始,将宽带相位抖动从157 ps RMS降至3.5 ps RMS,产生了一个适合通信和网络应用的高性能、低抖动的输出时钟。<上一页123

图5:比较带抖动的125 MHz系统时钟输入(黄色,顶部)与抖动清除后的输出时钟(蓝色,底部)实验测量该设计的相位噪声、相位抖动和抖动衰减的有效性。测量数据显示对正弦信号调制抖动的衰减可高达60dB,并导致综合相位抖动显著降低。图5显示抖动清除电路对时钟信号的影响;从一个能观察到明显抖动的125MHz系统时钟开始,将宽带相位抖动从157 ps RMS降至3.5 ps RMS,产生了一个适合通信和网络应用的高性能、低抖动的输出时钟。<上一页123 - 第一页:时钟振荡器和射频系统

- 第二页:频率控制方法及DCXO参数的选择

- 第三页:DCXO抖动清除电路实现