防DPA攻击的集成电路设计方法

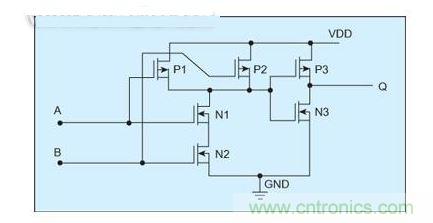

品慧电子讯与传统的攻击技术相比,差分功耗分析(DPA,Differential Power Analysis)攻击技术具有更强的攻击性和解密效率,因此防DPA攻击的设计方法越来越引起电路设计工程师的重视。本文从组合逻辑、寄存器、存储器、传输数据结构和中间状态等几个方面对防DPA攻击的电路设计方法进行了介绍。最近,一种DPA攻击技术被用来破译集成电路中的重要信息。DPA攻击技术的原理是:当芯片在执行不同的指令进行各种运算时,对应的功率消耗也相应变化。通过使用特殊的电子测量仪和数学统计技术,来检测和分析这些变化,从而得到芯片中的特定关键信息。这种利用指令的电流变化来分析密码算法和密码的方法,和以往的攻击技术有根本的不同,因此防DPA攻击的设计方法越来越引起电路设计工程师的重视。传统的防DPA攻击的方法有两种:一种是用随机数发生器产生额外的噪声和干扰信号,另一种是通过增加滤波电路来消除噪声。这两种方法都具有其固有缺陷,它们都会增加芯片的面积,其中前一种方法还会增加额外功耗,后一种方法则只是相对增加了DPA攻击的难度,并不能彻底解决DPA攻击问题。本文介绍的防DPA攻击的电路设计方法不同于传统方法,它从DPA的攻击原理出发,专门针对DPA攻击而设计,能有效解决通过分析芯片电流变化来进行攻击的问题。这种防DPA攻击的电路设计方法从分析集成电路的基本电路单元开始,由简到繁设计出防DPA攻击的复杂电路,从根本上解决了DPA攻击问题。防DPA攻击的基本电路单元一个典型的CMOS NAND电路通常由4个MOS管组成,包括2个PMOS管和2个NMOS管。图1是一个CMOS AND电路,它是由一个NAND电路(P1和P2的参数相同,N1和N2的参数相同)和一个NOT电路组成。

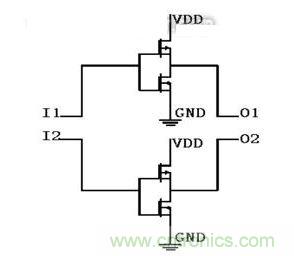

图1:CMOS AND电路由一个NAND电路和一个NOT电路组成由于P1和P2的参数相同,而且这两个晶体管是并行的,所以当输入信号A变化或者B发生变化时,这两个PMOS管对AND的瞬态变化的影响一样。而N1和N2是串行的,因此当输入A=1、B=0时,NAND的瞬态特性与输入A=0、B=1时的瞬态特性不同。虽然理想CMOS数字逻辑门在静态条件下不会消耗电流,但当输入信号变化时,它会消耗一定电流。这是因为MOSFET和信号传输线都存在寄生电容,并且当逻辑门处于变化状态时,Vdd和Gnd都存在瞬态电流。因此,这个与门的瞬态电流大小不仅与输入信号的变化有关,还与输出值Q有关。本文介绍的防DPA攻击的基本电路单元,对所有可能的输入信号都表现出相同的电特性。这些电特性包括导通和闭合的PMOS管和NMOS管的数量、输入线的电容负载、输出线的负载以及电路单元自身的瞬态电流。图2为该基本电路单元的电路结构。这个门电路有A和B两个输入,输入信号是2位的常数汉明权重码(constant Hamming weight representation),即A1和A2分别是0、1时对应“假”逻辑,1、0时对应“真”逻辑。在图2中,信号传输都是以2位汉明码形式进行,因此无论A和B信号如何变化,翻转的MOS管的数量都相同,且是一个常数10。

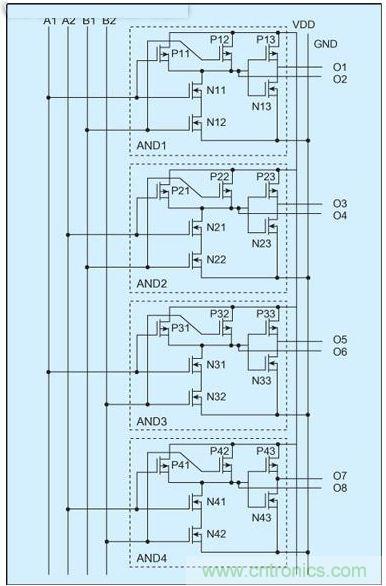

图1:CMOS AND电路由一个NAND电路和一个NOT电路组成由于P1和P2的参数相同,而且这两个晶体管是并行的,所以当输入信号A变化或者B发生变化时,这两个PMOS管对AND的瞬态变化的影响一样。而N1和N2是串行的,因此当输入A=1、B=0时,NAND的瞬态特性与输入A=0、B=1时的瞬态特性不同。虽然理想CMOS数字逻辑门在静态条件下不会消耗电流,但当输入信号变化时,它会消耗一定电流。这是因为MOSFET和信号传输线都存在寄生电容,并且当逻辑门处于变化状态时,Vdd和Gnd都存在瞬态电流。因此,这个与门的瞬态电流大小不仅与输入信号的变化有关,还与输出值Q有关。本文介绍的防DPA攻击的基本电路单元,对所有可能的输入信号都表现出相同的电特性。这些电特性包括导通和闭合的PMOS管和NMOS管的数量、输入线的电容负载、输出线的负载以及电路单元自身的瞬态电流。图2为该基本电路单元的电路结构。这个门电路有A和B两个输入,输入信号是2位的常数汉明权重码(constant Hamming weight representation),即A1和A2分别是0、1时对应“假”逻辑,1、0时对应“真”逻辑。在图2中,信号传输都是以2位汉明码形式进行,因此无论A和B信号如何变化,翻转的MOS管的数量都相同,且是一个常数10。 图2:防DPA攻击的基本电路单元的电路结构这个防DPA攻击的基本电路单元还可以表达多种逻辑。当需要表达AND逻辑时,输出为O1、O2,其中O1为汉明码指示位;当需要表达NAND逻辑时,输出为O2、O1,其中O2为2位汉明码指示位;当需要表达OR逻辑时,输出为O7、O8,其中O7为汉明码指示位;当需要表达NOR逻辑时,输出为O8、O7,其中O8为汉明码指示位。而O3、O4、O5和O6是没有作用的输出信号,但为保证各种输入情况下基本单元的对称性和相同性,这几个输出管脚在实际电路设计中应尽量和O1、O2、O7、O8接相同的负载。123下一页>

图2:防DPA攻击的基本电路单元的电路结构这个防DPA攻击的基本电路单元还可以表达多种逻辑。当需要表达AND逻辑时,输出为O1、O2,其中O1为汉明码指示位;当需要表达NAND逻辑时,输出为O2、O1,其中O2为2位汉明码指示位;当需要表达OR逻辑时,输出为O7、O8,其中O7为汉明码指示位;当需要表达NOR逻辑时,输出为O8、O7,其中O8为汉明码指示位。而O3、O4、O5和O6是没有作用的输出信号,但为保证各种输入情况下基本单元的对称性和相同性,这几个输出管脚在实际电路设计中应尽量和O1、O2、O7、O8接相同的负载。123下一页> - 第一页:防DPA攻击的集成电路设计方法(1)

- 第二页:防DPA攻击的集成电路设计方法(2)

- 第三页:防DPA攻击的集成电路设计方法(3)

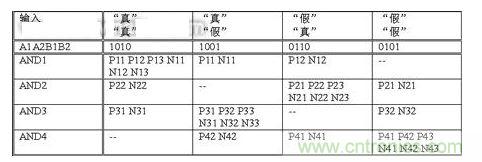

表1:无论输入信号是什么,基本电路单元中翻转的晶体管数量保持恒定在基本单元进行下一次运算之前,其所有输入值需要重新设置为0,这个操作使同等数量的晶体管翻转,攻击者将无法从功耗分析上看出先前的输入值。同样,如果将所有输入值设置为1也具有相同效果。本文把每次运算之间的设置初始值的操作状态称为“中间态”。多级组合逻辑的设计在实际电路中,多级的组合逻辑将串接在一起,即基本单元的输出端连接到下一级基本单元的输入端。在这种情况下,中间态必须能非常方便地在各级基本单元之间传输,以保证整个电路的不可攻击性。图3显示了一种可传输中间态的防DPA攻击的基本单元。

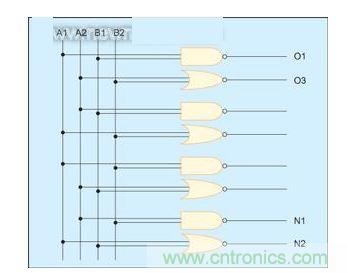

表1:无论输入信号是什么,基本电路单元中翻转的晶体管数量保持恒定在基本单元进行下一次运算之前,其所有输入值需要重新设置为0,这个操作使同等数量的晶体管翻转,攻击者将无法从功耗分析上看出先前的输入值。同样,如果将所有输入值设置为1也具有相同效果。本文把每次运算之间的设置初始值的操作状态称为“中间态”。多级组合逻辑的设计在实际电路中,多级的组合逻辑将串接在一起,即基本单元的输出端连接到下一级基本单元的输入端。在这种情况下,中间态必须能非常方便地在各级基本单元之间传输,以保证整个电路的不可攻击性。图3显示了一种可传输中间态的防DPA攻击的基本单元。 图3:一种可传输中间态的防DPA攻击的基本单元这种基本单元可以级连起来,连接成复杂的数字组合逻辑。该基本单元与图2描述的电路具有相同的逻辑特性,但当输入0000或者1111时,它的输出值是11或者00。输出值11或者00能对下一级的基本单元进行置位或者清零,这就实现了中间态的传输。<上一页123下一页>

图3:一种可传输中间态的防DPA攻击的基本单元这种基本单元可以级连起来,连接成复杂的数字组合逻辑。该基本单元与图2描述的电路具有相同的逻辑特性,但当输入0000或者1111时,它的输出值是11或者00。输出值11或者00能对下一级的基本单元进行置位或者清零,这就实现了中间态的传输。<上一页123下一页> - 第一页:防DPA攻击的集成电路设计方法(1)

- 第二页:防DPA攻击的集成电路设计方法(2)

- 第三页:防DPA攻击的集成电路设计方法(3)

图4:实现NOT逻辑的基本单元防DPA攻击的系统结构前面介绍了组合逻辑防DPA攻击的电路设计方法,现在将介绍时序逻辑防DPA攻击的设计方法及防DPA攻击的系统结构。举个例子,当电路传输的数据都是常数汉明权重码时,输入数据01给两位寄存器,当这两位寄存器的值是10时,两位寄存器都会翻转,而当两位寄存器的值是01时,两位寄存器都不会翻转。这个不同点会把有用信息泄漏给DPA攻击者。而在输入数据之前,先把寄存器设置为00或11,那么当输入数据是常数汉明权重码时,无论输入值是01还是10,都只有一个寄存器翻转,从运算状态到中间状态也只有一个寄存器翻转。这样可有效防止寄存器在数据传输过程中的信息泄漏。在有存储器的电路中,存储器在存储0或者存储1时有不同的电特性,如电流大小不同;同样,存储器在读取0或者读取1时也有不同的电特性,如电流大小不同。DPA攻击者会利用这个特性对芯片进行分析,所以必须保证在对存储器进行操作时有相同的电特性。现在,由于系统传输的是常数汉明权重码,所以在读取存储器的数据时,无论读取的是什么值,都具有相同个数的1和相同个数的0。例如当数据线是8位时,每次传输数据都有4位0以及4位1。同样,在存储数据时,无论存储的是什么值,只要是常数汉明权重码,都将存储相同个数的1和相同个数的0。这样,在所有存储器操作过程中都不会出现信息泄漏。以上从组合逻辑、寄存器、存储器、传输数据结构和中间状态等几个方面对防DPA攻击的电路设计方法进行了介绍和说明,而组合逻辑基本单元、寄存器、存储器等器件完全可以构成一个复杂的防DPA攻击的电路。为证明这种方法的有效性,对两种智能卡芯片进行了对比。这两种芯片都基于ISO/IEC7816协议,内部加密系统采用192位3DES来实现。一种芯片是采用普通的电路设计方法设计实现,另一种芯片在关键设计上采用了本文介绍的方法。用Cryptography Research 公司的DPA Workstation测试系统对前一种芯片进行分析,15分钟内就破译了芯片加密电路,取得密钥。而对采用本方法实现的芯片,则无法用DPA Workstation测试系统进行分析,因为该测试系统是基于数据在加密算法的运行中出现的电流/电源变化来获得密钥,而现在,它无法从电流/电源变化中取得任何有效信息,自然也无法破译芯片。<上一页123

图4:实现NOT逻辑的基本单元防DPA攻击的系统结构前面介绍了组合逻辑防DPA攻击的电路设计方法,现在将介绍时序逻辑防DPA攻击的设计方法及防DPA攻击的系统结构。举个例子,当电路传输的数据都是常数汉明权重码时,输入数据01给两位寄存器,当这两位寄存器的值是10时,两位寄存器都会翻转,而当两位寄存器的值是01时,两位寄存器都不会翻转。这个不同点会把有用信息泄漏给DPA攻击者。而在输入数据之前,先把寄存器设置为00或11,那么当输入数据是常数汉明权重码时,无论输入值是01还是10,都只有一个寄存器翻转,从运算状态到中间状态也只有一个寄存器翻转。这样可有效防止寄存器在数据传输过程中的信息泄漏。在有存储器的电路中,存储器在存储0或者存储1时有不同的电特性,如电流大小不同;同样,存储器在读取0或者读取1时也有不同的电特性,如电流大小不同。DPA攻击者会利用这个特性对芯片进行分析,所以必须保证在对存储器进行操作时有相同的电特性。现在,由于系统传输的是常数汉明权重码,所以在读取存储器的数据时,无论读取的是什么值,都具有相同个数的1和相同个数的0。例如当数据线是8位时,每次传输数据都有4位0以及4位1。同样,在存储数据时,无论存储的是什么值,只要是常数汉明权重码,都将存储相同个数的1和相同个数的0。这样,在所有存储器操作过程中都不会出现信息泄漏。以上从组合逻辑、寄存器、存储器、传输数据结构和中间状态等几个方面对防DPA攻击的电路设计方法进行了介绍和说明,而组合逻辑基本单元、寄存器、存储器等器件完全可以构成一个复杂的防DPA攻击的电路。为证明这种方法的有效性,对两种智能卡芯片进行了对比。这两种芯片都基于ISO/IEC7816协议,内部加密系统采用192位3DES来实现。一种芯片是采用普通的电路设计方法设计实现,另一种芯片在关键设计上采用了本文介绍的方法。用Cryptography Research 公司的DPA Workstation测试系统对前一种芯片进行分析,15分钟内就破译了芯片加密电路,取得密钥。而对采用本方法实现的芯片,则无法用DPA Workstation测试系统进行分析,因为该测试系统是基于数据在加密算法的运行中出现的电流/电源变化来获得密钥,而现在,它无法从电流/电源变化中取得任何有效信息,自然也无法破译芯片。<上一页123 - 第一页:防DPA攻击的集成电路设计方法(1)

- 第二页:防DPA攻击的集成电路设计方法(2)

- 第三页:防DPA攻击的集成电路设计方法(3)