专家支招:如何减少集成电路中的天线效应

品慧电子讯在集成电路的制造过程中,由于金属层暴露在外,导致上面聚集了许多静电电荷,从而会产生影响产品产量和可靠性的效应——天线效应。该效应在虽小,但是影响极大,严重的话会产生泄电,从而带来的损害更大。这里专家讲为大家详细的讲解如何如何减少集成电路中的天线效应 ,大家可以来参观学习。

如摩尔定律所述,数十年来,集成电路的密度和性能迅猛增长。众所周知,这种高速增长的趋势总有一天会结束,人们只是不知道当这一刻来临时,集成电路 的密度和性能到底能达到何种程度。随着技术的发展,集成电路密度不断增加,而栅氧化层宽度不断减少,超大规模集成电路中常见的多种效应变得原来越重要并难 以控制。天线效应便是其中之一。在过去的二十年中,半导体技术得以迅速发展,催生出更小规格、更高封装密度、更高速电路、更低功耗的产品。本文将讨论天线 效应以及减少天线效应的解决方案。

天线效应

天线效应或等离子导致栅氧损伤是指:在MOS集成电路生产过程中,一种可潜在影响产品产量和可靠性的效应。

目前,平版印刷工艺采用“等离子刻蚀”法(或“干法刻蚀”)制造集成电路。等离子是一种用于刻蚀的离子化/活性气体。它可进行超级模式控制(更锋利边 缘/更少咬边),并实现多种在传统刻蚀中无法实现的化学反应。但凡事都有两面性,它还带来一些副作用,其中之一就是充电损伤。

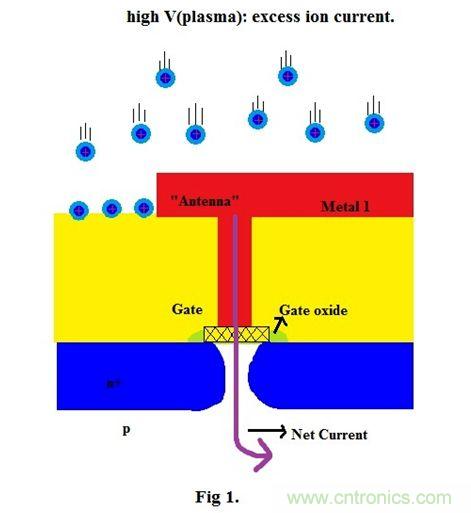

等离子充电损伤是指在等离子处理过程中,MOSFET 中产生的栅氧化层的非预期高场应力。在等离子刻蚀过程中,大量电荷聚集在多晶硅和金属表面。通过电容耦合,在栅氧化层中会形成较大电场,导致产生可损伤氧 化层并改变设备阀值电压(VT)的应力。如下图所示,被聚集的静电荷被传输到栅极中,通过栅氧化层 ,被电流隧道中和。

图1:等离子刻蚀过程中的天线效应。

显而易见,暴露在等离子面前的导体面积非常重要,它决定静电荷聚集率和隧穿电流的大小 。这就是所谓的“天线效应”。栅极下的导体与氧化层的面积比就是天线比率。一般来讲,天线比率可看做是一种电流倍增器,可放大栅氧化层隧穿电流的密度。对 于给定的天线比率来说,等粒子密度越高,隧穿电流越大。更高的隧穿电流意味着更高的损伤。

3种等离子制造过程

导体层模式刻蚀过程——累积电荷量与周长成正比。

灰化过程——累积电荷量与面积呈正比。

接触刻蚀过程——累积电荷量与通过区域的面积成正比。

天线比率(AR)的传统定义是指“天线”导体的面积与所相连的栅氧化层面积的比率。传统理论认为,天线效应降低程度与天线比率成正比(每个金属层的充电效果是相同的)。然而,人们发现天线比率并不取决于天线效应,还需要考虑布局问题。

1234下一页>

- 第一页:详解天线效应

- 第二页:布局对充电损伤的影响

- 第三页:减少天线效应的设计解决方案(1)

- 第四页:减少天线效应的设计解决方案(2)

布局对充电损伤的影响

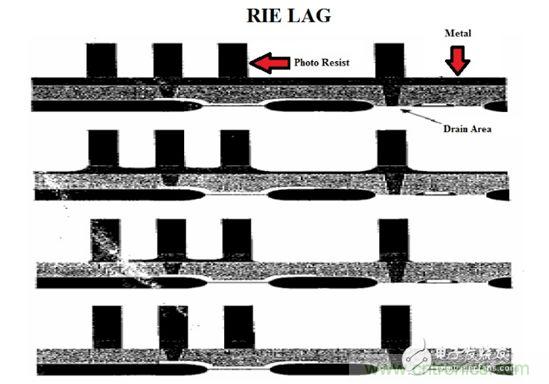

充电损伤的程度是一个几何函数,与极密栅线天线相关。但是由于刻蚀率的差异反映出的刻蚀延迟、等离子灰化和氧化沉积以及等离子诱导损伤(PID)的原因,使得充电损伤更容易受到电子屏蔽效应的影响。

图2:布局对充电损伤的影响。

因此,天线效应的新模式需要考虑刻蚀时间的因素,如公式1。而通过插入二极管或桥(布线)控制天线效应,可以更好地预测天线效应,如公式2所示。

![]()

其中, Q指在刻蚀期间,向栅氧化层注入的总积累电荷。

A为导电层面积,等离子电流密度J下的电容容量为C

a为栅极面积,等离子电流密度J下的电容容量为a

α为电容比

P为天线电容器的周长

p为栅电容器的周长

ω为等离子电源的角频率

根据基于PID的新模式,PID不取决于AR,但是天线电容与栅极电容的比例是PID的良好指标。PID取决于等离子电源的频率,当氧化层《4nm,PID将对应力电流变得不敏感。在不增加J的情况下,增加栅极的介电常数,可增加PID。

<上一页1234下一页>

- 第一页:详解天线效应

- 第二页:布局对充电损伤的影响

- 第三页:减少天线效应的设计解决方案(1)

- 第四页:减少天线效应的设计解决方案(2)

减少天线效应的设计解决方案

下面几种解决方案都可以用来降低天线效应。

1. 跳线法:通过插入跳线,断开存在天线效应的天线并布线到上一层金属层;直到最后的金属层被刻蚀,所有被刻蚀的金属才与栅相连。

2. 虚拟晶体管:添加额外栅会减少电容比;PFET比NFET更敏感;反向天线效应的问题。

3. 添加嵌入式保护二极管:将反向偏置二极管与晶体管中的栅相连接(在电路正常运行期间,二极管不会影响功能)。

4. 布局和布线后,插入二极管:仅将二极管连接到受到天线效应的金属层,一个二极管可保护连接到相同输出端口的所有输入端口。

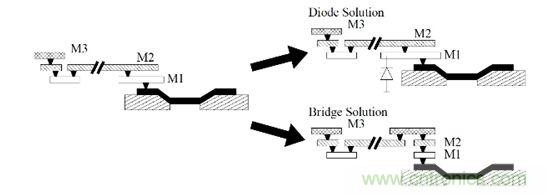

消除天线效应最重要的两个方法便是跳线法和插入二极管。接下来,我们将详细讨论这两种方法。跳线法是应对天线效应最有效的方法。插入二极管可解决其他天线问题。

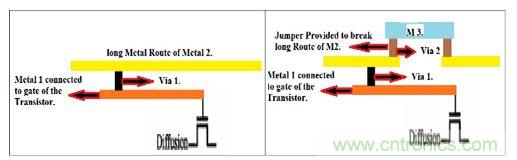

跳线法

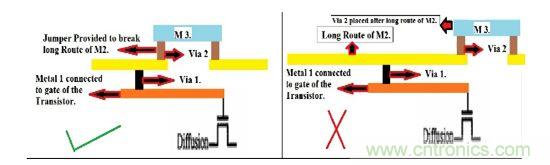

跳线是断开存在天线效应的金属层,通过通孔连接到其它金属层,最后再回到当前层。如下图所示,跳线法将很长的天线分成若干短天线,减小连接到栅输入的电线面积,从而减少聚集电荷。

图3:跳线法减少天线效应示意图。

需要注意的是,跳线的放置位置十分重要。必须把跳线放置在可减少布线长度的位置。下图可详细说明。如下图所示,在两张图片中,输入和输出引脚间都有同 样长度的间距,只是跳线位置稍有不同。第一张图的电路没有受到天线效应的影响,而第二张图中的电路却受到了天线效应的影响。

图4:在栅周围插入跳线。

通过这个例子可以很明显的看出,可使用跳线(又叫做“桥”)避免天线效应。跳线即断开存在天线效应的金属层,通过通孔将静电荷传送到更高一层的金属 层,然后再回到当前层。在金属化的过程中,除了在最高一层上,引脚与很小的电线面积相连接,避免该层以下的任何天线问题的发生。

<上一页1234下一页>

- 第一页:详解天线效应

- 第二页:布局对充电损伤的影响

- 第三页:减少天线效应的设计解决方案(1)

- 第四页:减少天线效应的设计解决方案(2)

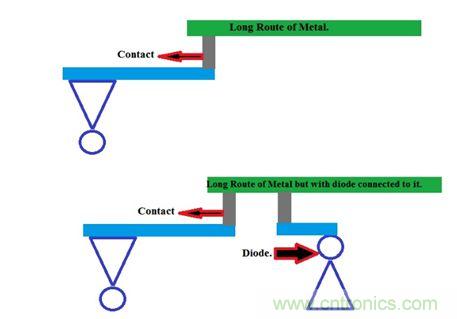

插入二极管

如图所示,在逻辑栅输入引脚旁边插入二极管,可为底层电路提供一个电荷泄放路径,因此累积电荷就无法对晶体管栅构成威胁。使用二极管可为通过基板聚集在金属层上的额外离子提供电荷泄放路径。

图5:在逻辑栅输入周围插入二极管。

然而,插入二极管会增加逻辑栅的输入负载,从而增大电路单元面积并影响时序。此外,空间狭小的地方不适合插入二极管。

图6:通过插入二极管或桥(布线)控制天线效应。

总结

在集成电路的制造过程中,由于金属层暴露在外,导致上面聚集了许多静电电荷。电荷的数量取决于很多原因,从天线的角度来说,电荷的数量取决于金属的暴 露面积。金属暴露的面积越大,聚集的电荷就越多。基板位于底部并与制造设器件连接,因此在栅氧化层产生一个电压梯度。当这个梯度变得足够大时,它将通过爆 炸性放电(即“闪电”)来释放。这个问题对小型技术领域产生非常大的影响,因为泄电所带来的损害很可能波及整个栅极。

由于表达天线比率方法并没有统一,因此对于每项加工技术而言,天线规则检查都不同。

可在需要受到保护的栅极旁边插入反向偏置二极管,避免电路遭受天线效应。在芯片正常运行期间,反向偏置二极管可防止电子在电路与二极管间流动,并防止 电子流向芯片基板。然而再制造过程中,电路上的电荷会聚集在某一点上,在这一点上电压会超过其承受限度。这一点上的电压高于电路正常运行的电压,但低于栅 极中可预期的静电放电电压。当这种情况发生时,二极管允许电子从电路中流向基板,因此缓解电路中累积的电荷。这是一个非破坏性过程,并且在制造过程中,电 路可通过二极管进行多次放电。

另一个避免遭受天线效应的方法是通过改变金属层对天线进行“切割”(即“跳线法”)。当该金属层被制成时,一侧的大片金属层不再电连接到栅极,因此不 会产生天线效应。当通过更高级金属“桥”进行连接时,导体表面不再暴露在外,因此不会收集游离电荷,从而避免天线效应。