实现逻辑分析仪成功探测的6项提示

中心议题:

- 实现逻辑分析仪成功探测的6项提示

为了完成今天越来越复杂的数字系统的设计, 工程师需要完善的分析工具。对于系统验证任务, 大多数工程师都要依靠逻辑分析仪。随着被测系统速度的不断提升和复杂程度的持续增加, 逻辑分析仪厂商也及时提高了仪器的性能和功能, 以满足工程师的需求。在许多情况下, 逻辑分析仪主机的性能往往超过手头任务的需要, 而从分析仪到目标系统的探头物理连接则成为系统性能的瓶颈。如果逻辑分析仪接收到的信号有畸变, 那么逻辑分析仪的强大触发和分析工具将是无用武之地。

这篇应用指南将讨论实现成功逻辑分析仪探头连接, 需要考虑的探测问题。我们将介绍探头结构形式选择、探头负载和信号质量概念, 以及与接地有关的常见问题。最后讨论两种容易犯的错误: 在错误的引线位置探测和选择了错误的互连。

提示1探头结构形式

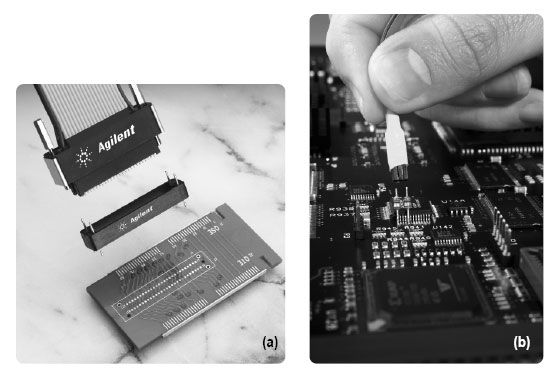

如果您决定使用逻辑分析仪, 也就必须选择使用何种类型的探头连接。探头连接可分成两大类: “设计中包括连接”和“事后连接”。对于设计中包括的连接, 逻辑分析仪探头所探测的测试点就融入在最初设计中。连接器探头和无连接器探头都属于这类连接。为使用这两类探头,设计师在电路板上布放适宜的焊盘,并把感兴趣的信号连到焊盘上。逻辑分析仪探头上的连接器能与目标连接器可靠插接。无连接器探头则能压在电路板焊盘上, 以保证良好地接触 (图1a)。

探头 “事后连接” 的适应测试能力未融入设计的系统。此时您需要用包括各种互连附件(焊接、抓钩等)的探头触针实现连接。最常用的“事后连接”探头是飞线探头(图1b)。

在讨论各种探头结构形式的优缺点前, 先了解您在把逻辑分析仪接到系统时会遇到的一些问题。

图1. 这些照片对“设计中包括连接”的探头和“事后连接”的探头进行比较。

提示2探头负载

您要设法尽可能减小探头对系统呈现的电气负载。如果探头极大改变了系统性能, 它就不能帮助您验证系统; 因为故障可能完全是因探头引发。负载主要有两方面影响。首先是降低目标电路板上的信号质量, 并进而导致系统故障。其次是降低送入逻辑分析仪的被观察波形质量。这会在验证中导致错误的否定结论。为避免这些问题, 您必须了解探头的结构。

逻辑分析仪探头有高输入阻抗。探头触针电路包括一个20kΩ量级的触针电阻器。低频时的探头阻抗接近该阻值。随着频率的上升,探头的寄生电容开始降低它的阻抗。阻抗沿标准RC响应滚降。这可能造成目标系统的问题; 当探头阻抗开始接近系统阻抗时, 由探头构成的电压分压器起着实质性的作用。低阻抗将吸收大量电流, 从而造成系统故障。

探头中的电容主要与连接器有关。例如若目标信号与探头触针电阻间有大的连接器, 该连接器就会把大电容加到探头负载中。使用小的连接器可减小这一电容量。

无连接器探头提供较低的电气负载。如前所述, 当您使用无连接器探头时, 就要在目标系统上放置承载焊盘。逻辑分析仪探头压着在目标小电路板上实现电气连接。由于消除了电气路径中的物理连接器, 就能实现非常低的电容量 (见表1)。

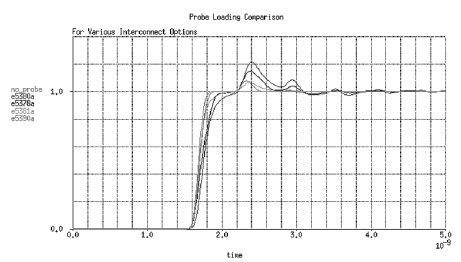

图2 显示负载端接传输线上各种探头结构形式对等效集总电容的影响。波形显示来自探头的电容性反射如何在初始波形后某一时刻到达接收器。123下一页> 关键字:逻辑分析仪 逻辑分析仪使用 逻辑分析仪测试 本文链接:http://www.cntronics.com/public/art/artinfo/id/80011337

E5380A Mictor连接器 3.0 pF E5378A Samtec 连接器 1.5 pF E5381A 飞线 (焊接) 0.9 pF E5390A 软触无连接器 0.7 pF

表1.

图2. 波形是比较各种互连探头负载的好方法。负载随连接器尺寸的减小(或消除)而减小。系统的原上升时间是150ps。

提示3探头触针处的信号质量

如前所述, 探头导致进入逻辑分析仪中的信号质量变差,从而得出错误的否定结论。这是验证者遇到麻烦的原因, 因为他们把大量时间用在调试并不存在的问题上。为避免这一问题, 您必须注意探头触针处的信号质量。

除了留意探头的电容性负载外,您还必须注意探头位置。这在选择各种不同端接方案时尤为重要。对于某种特定的端接方案, 接收器观察的信号可能有足够好的信号质量, 但在连线任何其它点观察到的信号却可能无法接受。

为说明这一点, 先来分析串联端接传输线理论。感应波形瞬间在源端电阻和导线特性阻抗间分开。半幅度的电波沿传输线传输到接收器。在到达接收器时经过 100% 的正反射, 把半幅信号加倍得到原波形的幅度。该反射波以相反方向在传输线

上传输, 直到被源端电阻器吸收, 从而结束瞬态响应。

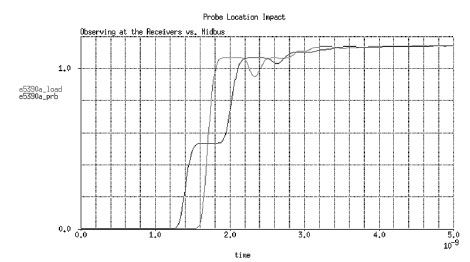

虽然这种方案为接收器提供一个良好的波形, 但该波形在传输线上呈阶梯形状。阶梯波形不适合逻辑分析仪, 因为逻辑分析仪不能确定波形半幅度期间到底是逻辑“1”还是逻辑“0”。图3显示这种情况的波形。注意接收器处的波形信号质量良好,而在探头触针处观察到的波形却无法接受。随着信号速度的增加, 探头触针处的信号质量对于成功的测量变得尤为重要。

图3. 在接收器处和在探头触针处观察到的串联端接系统波形。

注意在连线中间处观察到的波形阶梯形状。它表明正向传输的半幅度波形是往接收器方向传输。反向传输间反射波形与正向传输波形叠加后得到其最终值。

提示4接地问题

您在使用逻辑分析仪时需留意接地是否良好。探头的接地信号是被观察信号的参照。电气信号必须有它的返回电流路径。通常认为返回路径是具有零电阻的理想导体。如果不是这种情况, 接地返回路径阻抗上就有电压降。这一电压降将降低逻辑分析仪看到的电压幅度。当把探头接地时, 您的目标是提供尽可能低阻抗的返回路径 (或地连接)。从而使逻辑分析仪能够观察到原信号幅度。

地线过长是引起问题的常见原因。长地线的等效串联电阻造成跨该阻抗的压降。为避免这一问题, 地线长度不应超过信号线过多。大致相等的长度能使信号路径和接地路径中的寄生电阻相匹配。

另一常遇的探测问题是接地回路的自感。在地线和信号线构成环路时, 接地路径将产生正比于回路面积的自感。由于电感器感抗与频率相关, 所以这一电感会使系统带宽变窄。在高频时, 因电感阻止电荷快速过地线从而减小带宽。为缓解这一问题, 应让地环路尽可能小。使用连接器探头或无连接器探头时, 地环路大小通常已被确定。但飞线探头是通过普通导线把探头接到系统。此时有可能构成大的地环路。为避免产生地环路, 要把地线和信号线拧在一起构成双绞线。大多数飞线探头带有双绞线附件,能帮助解决这一问题。

不足的接地线数量也能导致探测问题。某些探头 (如飞线探头)是由使用者确定接地线数量。为理解这一问题, 以有16 个信号线,而仅有一个接地线的飞线探头为例。此时所有16个信号的返回电流都必须通过这一个接地连接。在一个或二个信号返回时, 接地线的自感是足够低的, 能够避免跨地线的电压。但对于16 个信号, 电流已大到足能产生不可忽略的电压。

解决这一问题需要增加接地线数。在理想情况下一个信号有一个接地。所需要的接地数与频率成正比。我们建议一个接地不要用于两个以上信号。如果您在用逻辑分析仪捕获数据时发现有问题, 首先要检查接地线数。<上一页123下一页> 关键字:逻辑分析仪 逻辑分析仪使用 逻辑分析仪测试 本文链接:http://www.cntronics.com/public/art/artinfo/id/80011337?page=2

提示5在错误的连线位置探测

常犯的错误

虽然今天有各种可用的探测选择, 但往往很难确定何种连接方案能确保成功。有时甚至难以知道到底可用哪种方案。下面的例子说明在选择了不适合您应用的探测解决方案时经常出现的两个问题。

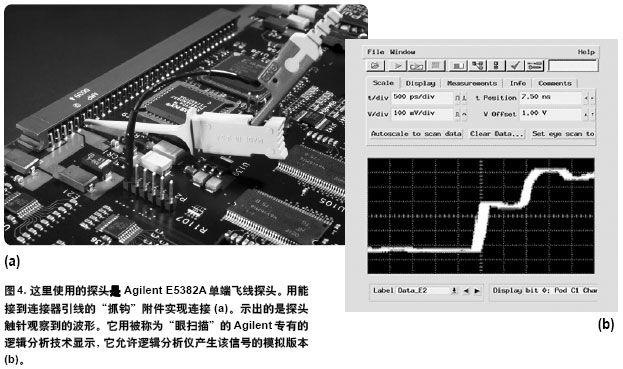

回到前面讨论的串联端接系统。该系统用背板上的驱动器IC和BGA封装的接收器实现。为方便起见, 使用者选择在背板连接器引脚处探测信号。但我们在前面已经说到, 在驱动器处探测串联端接系统会在逻辑分析仪的探头触针处产生阶梯波形。图4a示出该连接方案, 图4b示出逻辑分析仪观察到的波形。

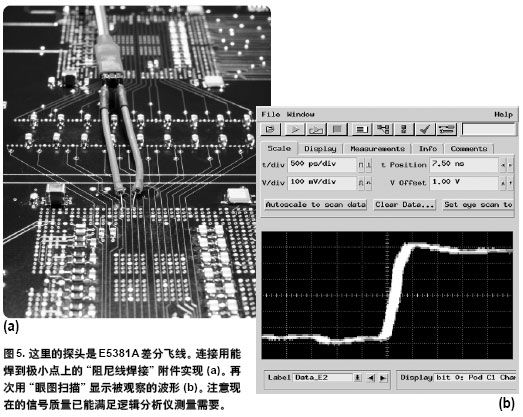

这一波形显然是无法接受的。解决方案是把探头直接放在接收器上。对BGA封装的最近物理探测点是电路板背面通过焊盘的引出口。图5示出新的连接方案, 它把飞线直接焊到BGA的通孔。此时得到的信号质量如图5b 所示。

提示6选择了错误的互连

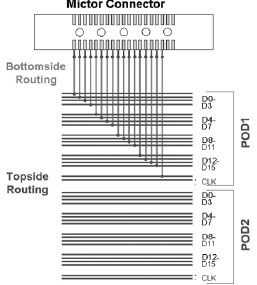

考虑逻辑分析仪观察到的是在电路板两个元件之间的信号。该信号在电路板外层, 不超过3.5pF 的负载不会导致系统故障。设计师决定用基于Mictor 连接器的探头 (AgilentE5380A)观察信号。由于连接器的出脚和结构要求, 信号不能直接接到连接器上。这就迫使设计师把连接器放在走线面, 而为每一信号另增通孔连接。从而需要在电路板另一层上经过与原信号相垂直的走线实现至连接器的连接。图6是这一连接的走线图。

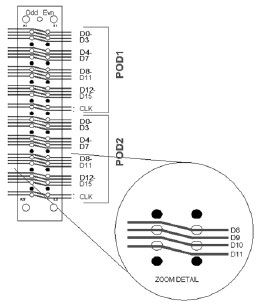

现在考虑使用Agilent E5390A软接触无连接器探头的替代解决方案。此时, 您可把信号直接穿过探头压着点焊盘 (图7)引入逻辑分析仪。采用这种方法, 系统就不会有附加的走线电容。探头的净电容是0.7pF。通过使用这种类型的连接方案, 您就能在不影响系统正常工作的条件下对电路进行分析。

图6. 该连接方案用基于Mictor 连接器的探头观察总线信号。注意连接Mictor 需要另外增加走线长度。这就把走线电容 (3pF) 加到了连接器上。这一连接的净电容已大于3.5pF,从而造成系统故障。

图7. 这里是用软接触无连接器探头观察总线信号。减小的探头负载和直接穿过压着点的走线实现了可接受的逻辑分析连接。

探头负责逻辑分析仪与您被测系统间的物理连接。在某些情况下探头会成为性能的瓶颈。如果逻辑分析仪接收信号有畸变, 那么逻辑分析仪的强大触发和分析工具将无用武之地。只有选择正确的探头结构形式, 采取最小化探头负载的措施,保证探头触针处的信号质量, 才能把信号畸变减到最小。特别要注意接地的好坏,它会使结果大不相同。

<上一页123 关键字:逻辑分析仪 逻辑分析仪使用 逻辑分析仪测试 本文链接:http://www.cntronics.com/public/art/artinfo/id/80011337?page=3