BSD技术特性与应用

中心议题:

- BSD技术动向

- BSD的制作技术

- BSD电子源的特性

- BSD的产品应用

- 使用寿命长,可靠性高

- 低分散电子释放角度电子释放能量大

- 电子垂直发射,不需收敛电极

- 电子释放稳定均匀无poppingnoise

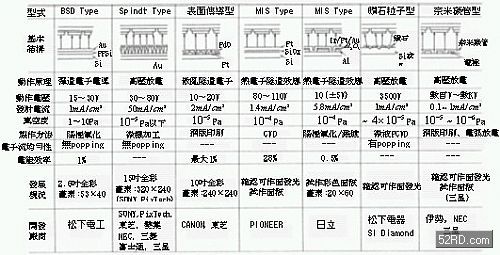

然电浆显示器(plasma)与LCD(LiquidCrystalDisplay)等平面显示器(FlatPanelDisplay)已经进入商品化阶段,不过耗电量、辉度、对比以及动画反应时间等问题,若与传统CRT比较时仍有改善的空间,另一方面有机EL等诸多新世代平面显示器(表1)却面临制程、成本、使用寿命、大型化等瓶颈,因此至今仍无法实用化。有鑑于此松下电工与东京农工大学利用BSD(BallisticelectronSurfaceemittingDevice)概念制作场发射显示器(FED:FieldEmittingDisplay)。

而BSD的动作原理是利用固体中的电子在近乎真空环境加速移动。该物性是由硅结晶奈米(nano;1nano=10-12m)结晶化形成鍊锁结构,由于鍊锁结构能垂直发射电子,因此利用电子该撞击前方涂有萤光体的透明基板产生影像。奈米技术制成的BSD可以有效解决平面显示器常见的问题,同时还具备低成本、制程简单、可大型化等优点,因此它的应用受到相关业者高度重视

表1各种FED平面显示器的动作原理与特性

BSD技术动向

BSD是应用弹道电子释放特性构成冷阴极电子源,它的电子释放原理不同于传统FED。表2是BSD代表性特徵,由表2可知BSD具有低电压驱动、低真空动作环境、不需集束电极、低制作成本等特性,尤其是玻璃基板与500°C低温湿制程(wetprocess),更可大幅降低制作成本。

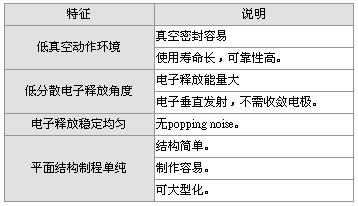

特征说明

低真空动作环境真空密封容易

使用寿命长,可靠性高。

低分散电子释放角度电子释放能量大

电子垂直发射,不需收敛电极。

电子释放稳定均匀无poppingnoise。

平面结构制程单纯结构简单。

制作容易。

可大型化。

表2BSD的特征

12345下一页> 关键字:BSD技术 FED 硅结晶奈米 本文链接:http://www.cntronics.com/public/art/artinfo/id/80005404

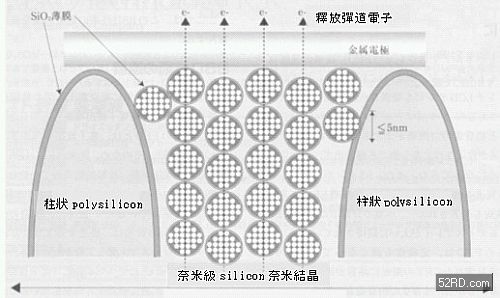

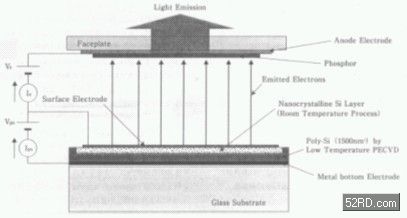

BSD是将silicon奈米结晶化形成锁鍊状结构,藉此使电子呈弹道状移动,一般将此现象称为弹道电子输送。图1是BSD电子源的动作机制说明图,基本上它是在柱状polysilicon之间形成电子drift层,polysilicon与奈米结晶silicon混合的systemunit称为NPS层(NanocrystallinePoly-Siliconlayer),虽然NPS层是利用阳极氧化技术制成,不过在polysilicon的结晶粒界的glen部位会产生快速反应,因此polysilicon结晶粒的表面,支配性形成奈米结晶silicon,使得NPS层内残留的silicon结晶粒比奈米结晶silicon多,该残留的柱状polysilicon可帮助散热,进而提高冷阴极的电子热传导稳定性,所以BSD释放电子时几乎不会产生闪烁噪讯(flickernoise)。

BSD释放电子时是利用电子作热激发,使电子从基板下方注入NPS层,由于奈米结晶silicon的表面,是利用低温氧化制程制成氧化薄膜,因此施加的电压几乎全部流入该氧化膜层内进而形成强电界领域,而氧化膜的厚度非常的薄,所以电子很容易将强电界领域的氧化膜变成tunnel,并进入邻接的奈米结晶silicon内,随着电子通过氧化膜被加速,并朝向表面电极方向前进,如此反覆相同动作所以到达表面附近的电子,具备比热平衡状态更高的运动能量,而表面电极也变得很容易将成为tunnel的电子释放至真空中。

BSD具体动作原理如图1所示,BSD电子源是先在由负极(cathode)所构成的背面基板上制作复晶硅膜(poly-Silicon),之后将复晶硅膜多孔化(porous),接着在复晶硅之间制作复数的微结晶硅,同时将复晶硅与微结晶硅的表面氧化,多孔化复晶硅(PPS:PorousPolySilicon)膜层厚度约1.5μm,最后在PPS表面制作Au或Ag等金属薄膜形成二极体(diode)结构,除了以上的差异PPS外部电子发射源的动作原理则与传统的FED完全相同,换句话说这种BSDtype的FED,也是利用电子撞击正面基板表面上的萤光体产生影像,它与以往的FED最大差异处,是电子发射源的制作方式与结构不同而已。

图1BSD的动作原理

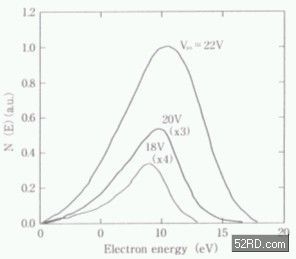

图2是释放至真空中的电子能量分佈量测结果,图中的x轴为电子能量,y轴为释放电子的相对数,测试时的基准能量是比照真空状态时的准位,测试方法是在室温下进行,採用一般性的交流减速电界法。假设表面金属的动作关数为ψ(eV)时,完全未发生冲突释放出去的电子最大能量,理论上几乎等于施加电压减去动作关数ψ的能量,以图2为例假设VPS=22V时,虽然分佈的最大能量-Vmax祇有17eV,不过表面电极的动作关数大约有5eV,换言之它与上述施加电压减去动作关数的结果完全一致,由此验证BSD具有独特的弹道电子释放特性。实际上在室温环境下NPS层多少会发生冲突,一般是将它视准弹道电子的释放。

如图2所示的能量分佈峰值位置,亦即电子数最多的能量,理论上是最大能量的60%约在10eV处,即使如此若与其它种类的电子源比较时,很明显的是BSD具备很高的能量。另一个特殊现象是该能量分佈与施加电压具有依存性,也就是说随着VPS的增加,峰值能量Emax与最大能量会逐渐移至highenergyside,这意味着BSD释放的电子在NPS层几乎未散乱,如果在低温环境下测试释放电子的能量分佈,上述弹道电子释放更加明显,而且能量分佈幅度更加狭窄(峰值能量EP朝最大能量Emax方向移动)。

图2BSD释放电子能量的特性

综合以上的说明可知BSD的电子释放机制,是当电压注入上方电极与背面基板之间时,下方铝质电极所产生的电子会注入PPS层内的微结晶硅,而电子通过微结晶硅内部时几乎没有能量损耗(energyloss),主要原因是一旦施加电界后,微结晶硅表面的氧化膜会使电子加速。此外一般硅内部的平均自由行程约为50nm,而微结晶硅的glensize祇有5nm。由于当电子通过PPS层时,几乎不会与其它电子或硅原子发生冲突,因此电子通过微结晶硅内部时,能量损耗几乎等于零,使得到达上方金属电极的电子能量减去金属的动作关数值最大可达14~15eV,这种现象称为弹道电子传导效应。以往的弹道电子传导效应必需在真空环境下才会发生,不过BSD利用多孔化(porous)将复晶硅膜(polysilicon)包覆,因此它可在固体中产生弹道电子释放现象。利用这样的特性制作FED时可使已加速的电子,在cellgap内部呈垂直状发射出,并使电子撞击正面基板表面上的萤光体产生影像。由于BSD的电子发射源可将电子呈垂直状发射出去,因此cellgap高达数mm的高电压型FED,也不需要设置电子束收歛电极防止失真(crosstalk)现象。

<上一页12345下一页> 关键字:BSD技术 FED 硅结晶奈米 本文链接:http://www.cntronics.com/public/art/artinfo/id/80005404?page=2

BSD的制作技术

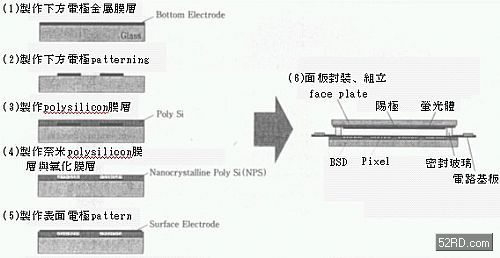

图3是BSD的基本结构,如图所示BSD电子源呈夹心状(sandwich)。图4是BSD的制作流程,由图可知下方电极pattern通常是利用溅镀法制作,基于量产性的考量因此BSD改用liftoff方式制作,接着在上方制作柱状polysilicon,虽然polysilicon可在amorphous膜层长膜,再利用雷射作退火处理进行再结晶化,不过如此一来polysilicon膜层厚度较厚,因此BSD採用减压CVD技术制作最佳化柱状polysilicon。一般CVD技术需在650°C左右高温下,利用石英玻璃才能获得polysilicon,基于成本与量产性的考量改用电浆(plasma)CVD技术,使长膜温度降至550°C以下,使用的玻璃则与TFT、PDP常用的玻璃相同。有关BSD的电子释放部的阳极氧化制程,主要是利用松下电工开发的阳极氧化?低温氧化一贯作业的湿制程(wetprocess)专用设备(图5),该设备具有低制作成本、可大型化、高良品率等特徵。

图3BSD的结构

图4BSD的制作流程

图5阳极氧化?CEO专用设备的外观

接着在玻璃基板上制作金属电极,并将金属电极上方的柱状polysilicon膜层浸泡于氟酸与乙醇混合液内,同时施加电压至混合液内的白金负极,与polysilicon膜层的正极,进行类似电界研磨加工。由于silicon在某些条件下无法进行研磨,反而会产生silicon的奈米结晶,这种特殊现象主要是因为柱状polysilicon的grainboundary的结合能量很低,使得该部份发生反应析并出silicon,在此同时被析出的silicon会进行再结晶化,最后形成如图1所示的奈米结构,这种被称为自我组织的独特现象发生与否,完全取决于制程条件的设定。

<上一页12345下一页> 关键字:BSD技术 FED 硅结晶奈米 本文链接:http://www.cntronics.com/public/art/artinfo/id/80005404?page=3

在柱状polysilicongrain之间形成奈米结晶polysilicon之后,去除洗净氟酸与乙醇,再注入以硫酸为base的电解液,并对白金负极与基板正极施加电压,藉此在奈米结晶polysilicon的表面形成很薄的氧化膜,这种称为电气化学的氧化法(ECO:ElectroChemicalOxidation)可以使大size的silicon结晶更容易氧化,最先开始氧化部位是polysilicongrain部份,接着是奈米结晶部位被氧化,最后是size比较均匀的奈米结晶部位,此时polysilicon部位会被很厚的氧化膜包覆,由于表面的polysilicon膜层也被很厚的氧化膜包覆,所以可以防止polysilicon膜层与表面电极的发生breakdown现象。

利用ECO制程形成氧化膜后立即进行清洗、干燥、溅镀,接着进行表面电极与电极patterning,便完成所有BSD电子源的作业流程。

在所有制程当中祇有polysilicon长膜时需要550°C高温之外,其它制程包含奈米结晶硅长膜与氧化膜的制作,都是在常温环境下进行,因此材料的高温履歷非常少,更无基板升、降温时间,所以可大幅缩减制作时间与制作成本,也就是说上述制程非常适合大尺寸面板的制作。

BSD电子源的特性

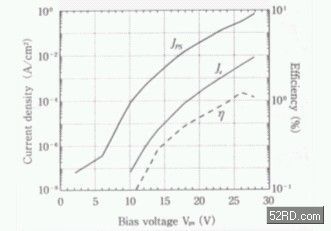

图6是典型的BSD电子源的电压?电流特性图,图中的横轴为电压,纵轴为电流密度,JPS是二极体(diode)的电流密度,JPS表示从二极体表面金属膜层释放至真空中的电子emission电流密度,一般emission电流祇能在VPS为正方向时才能观测到。由图可知随着电压增加,二极体的顺向电流与释放电流亦增大,当顺向电压为28V时emission电流密度约为8.9mA/cm²,emission效率约为1.2%左右。

图6BSD电子源的V-I特性

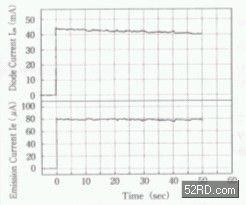

图7是BSD电子源的emission电流时间变化特性图,横轴为时间,纵轴为电流密度,二极体电压为16V,如图所示二极体电流IPS与释放电流Ie,不会随着电流发生spike,亦即所谓的闪烁(flicker)现象,显示BSD电子源不需外部电路,就可获得传统Spendtype电子源无法达成的特性。

图7二极体电流与释放电流的V时间变化特性

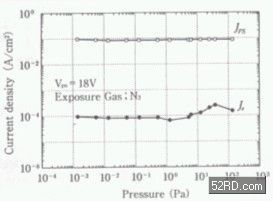

图8是BSD电子源的周围真空度发生变化时的emission电流变化特性,具体测试方法是将炉内更换成氮素,接着抽真空至10-4Pa再逐渐导入氮素,藉此观察真空度变化时的emission电流变化,图中的横轴为真空度,纵轴为二极体(diode)的电流密度,由图可知即使真空度降至10-4,emission的电流密度几乎无任何改变,显示BSD电子源在真空度非常恶劣的环境下,仍具备良好的emission特性。

图8BSD电子源的释放电流与真空度依存性

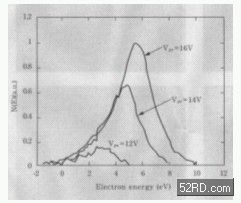

图9是二极体电压Vps对电子能量及释放电子数量关系图,由图可知电子能量随着Vps变大而增加,例如Vps为16V时可获得6eV值,如此高的电子能量相当于CRT或传统(convention)FED的100倍左右。目前BSD之FED的电子释放效率约为1%,电流释放密度最大是1mA/cm2,因此已经足够撞击正面基板表面上的萤光体,并获得极高的发光效果。此外BSD之FED祇需20V左右的动作电压,如果换算成42吋的FED时,它的电力消耗量约为100W左幼,是同级电浆显示器(PDP:PlasmaDisplayPanel)的1/3左右。

图9diode电压与电子能量与电子释放数量之关系

BSD非常适用于高电压SpendtypeFED。由于BSD具有垂直弹道电子释放特性,因此不需要收歛电极来控制电子束的发射角度,这对降低FED的制作成本具有重大的影响,除此之外BSD技术赋与spacer更宽广的选择裕度。以往的FED都是利用spacer使cellgap能维持一定的间隙,因此选用spacer时除了粒径均匀性与稳定性的考量之外,spacer还需要具备不会干涉电子束飞行轨道重要特质,然而不论基板材质为陶瓷(ceramic)或是玻璃(glass),spacer都会因施加电压而带负电,进而直接、间接影响电子束的飞行轨道,造成萤光体撞击点偏移、影像画质劣化等不良现象。

<上一页12345下一页> 关键字:BSD技术 FED 硅结晶奈米 本文链接:http://www.cntronics.com/public/art/artinfo/id/80005404?page=4

由于BSD的弹道电子释放现象所产生的电子发射角度几乎是无偏差的垂直角,因此BSD的FED可无限制的选用适用的spacer。如上所述BSD最大特点(advantage)是它的制作性,传统高电压型FED的发射电极(emitting)是先制作发射平台(hall),再制作Al2O3与Wo、Ni等覆盖层(scapegoatlay)垂直膜层,最后利用蚀刻(etching)技术去除覆盖层,相较之下BSD之FED的电子发射源祇需制作复晶硅膜,之后再经过膜层多孔化与氧化等制程即可,如此简易的制程对平面显示器(FPD:FlatPanelDisplay)大型化与低价化具有加乘效应。

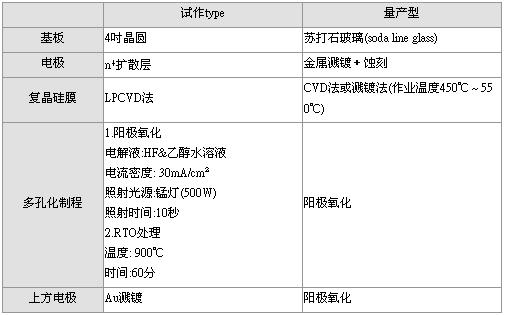

表3是负极基板的制作流程,表中左侧是利用BSD试作FED的制程条件,右侧是未来商品化时的预定制造方法。

※试作type的流程如下所示:

1.先以LPVCD制作复晶硅膜。

2.HF:再用乙醇(Athanol)作阳极氧化。

3.最后以RTO(RapidThermalOxidation)将复晶硅膜氧化。

※未来商品化时的预定制作流程如下所示:

1.先以溅镀法(sputter)在苏打石玻璃(sodalineglass)制作Al等膜层,再用蚀刻法(etching)制作图样(pattern)。

2.接着利用CVD或蚀刻技术制作复晶硅膜。

3.以电解电镀技术进行阳极氧化处理制作微结晶硅。

4.最后溅镀Au或Ag等金属。

上述第1与第4项之流程系使用现有的成膜技术与材料;第2与第3项则为松下公司开发的多孔化PPS技术。有关第2项复晶硅膜制程必需将作业温度与压力等参数作最佳化组合,如此便可使苏打石玻璃在450°C~550°C的低温环境下完成长膜作业。第3项的电解液、液温、电流密度等参数经过作最佳化后,在一定条件下进行阳极氧化,之后必需再度更改制程参数(processparameter)才可再进行阳极氧化作业。

虽然第2与第3项制程稍嫌烦琐,不过并未涉及高单价材料或是高难度作业,祇需稍为修改或是延用现有的复晶硅制作技术与TFT-LCD生产设备即可。此外微结晶硅的glensize与porous的幅宽,可透过制程参数自由控制调整,因此类似要求有高细画质的spindttype的FED发射体(emitter),每一dot可设置超过100个以上的PPS。

BSD的产品应用

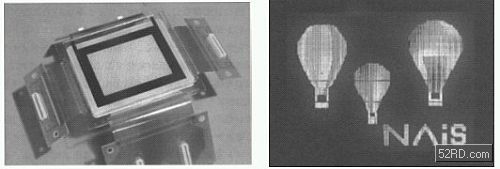

如上所述BSD电子源具有非常独特的性能,因此利用BSD与低温制程试做2.6吋,168(RGB)×126全彩BSD平面显示器。126根下方电极是在玻璃基板上以溅镀方式制成,上方形成polysilicon之后立即进行阳极氧化与CEO制程,接着利用蒸镀法制作表面电极,使表面电极与下方电极形成直交状,然后再以离子研磨法(ionmilling)进行168×3的patterning,最后介由spacer将frontglass粘贴于BSD电子源。

有关frontglass它是先在玻璃基板coat一层ITO,再以网版印刷法依序将P22萤光体、blackmatrix与RGB各色均匀覆盖,frontglass与BSD电子源间隔约3mm,当6kV的DC电压施加于表面电极之间时可使释放电子加速,由于BSD电子源与frontglass之间不需电子收敛用grid电极,因此利用溶融玻璃密封后进行10-4Pa抽真空,便可获利BSD平面显示器。驱动BSD显示器是依序使每个line的BSD电子源加速发生emission,负极扫描速度为每秒30次,表面电极与下方电极之间施加VPS=22V的资料脉冲。

图10表4分别是利率BSD技术制作之2.6吋彩色FED外观图与规格;由于BSD的电子发射源可在大cellgap环境下,以垂直方式在涂有萤光体的面板上产生图样(pattern),因此祇要驱动电路与驱动方式经由最加化设计,便可获得令人满意的影像显示效果。

图10利用BSD制作2.6吋全彩之FED外观

表4全彩BSD的FED规格<上一页12345 关键字:BSD技术 FED 硅结晶奈米 本文链接:http://www.cntronics.com/public/art/artinfo/id/80005404?page=5