运算放大器参数测试有哪些方法?

【导读】一款单个测试电路可“执行对任何运算放大器全面检查所需的所有标准DC测试”。单个测试电路在那个时候可能够用,但今天并非如此,因为现代运算放大器具有更全面的规范。因此,单个测试电路不再包揽所有DC测试。

一款单个测试电路可“执行对任何运算放大器全面检查所需的所有标准DC测试”。单个测试电路在那个时候可能够用,但今天并非如此,因为现代运算放大器具有更全面的规范。因此,单个测试电路不再包揽所有DC测试。

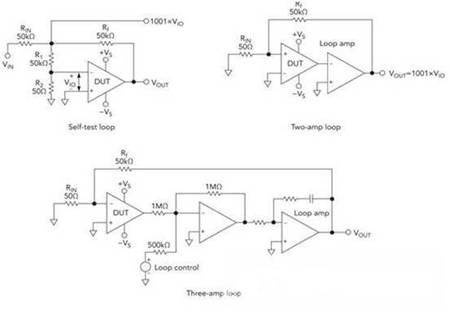

现在经常使用三种测试电路拓扑对运算放大器DC参数进行工作台及生产测试。这三种拓扑为(1)双运算放大器测试环路、(2)自测试环路(有时称故障求和点测 试环路)和(3)三运算放大器环路。您可使用这些电路测试DC参数,其中包括静态电流(IQ)、电压失调(VOS)、电源抑制比(PSRR)、共模抑制比 (CMRR)以及DC开环增益(AOL)。

静态电流

静态电流是指器件输出电流等于零时其所消耗的电流。尽管IQ测试看起来相当简单,但也必须注意确保良好的结果,尤其是在处理极高或极低IQ部件时。图1是可 用来测试IQ及其它参数的三种实用电路,其必须考虑若干负载电流情况。这包括测试环路中的反馈电流。实际上,反馈电阻器Rf也能给器件带来负载,影响IQ 测量。

图1 这三款电路可用来测量静态电流(IQ)

我们以测试OPA369运算放大器为例来说明这些电路。该部件的静态电流是每通道1μA。输入失调电压为750μV。图1中的双运算放大器环路电路 可为被测试器件的输出提供750.75mV 的电压。这种输入电压可使Rf通过15μA 的电流。该电流来自电源,会给任何测量增加误差。因此在进行IQ测量之前,必须采取措施确保输出电流真的等于零。

自测试电路不是测量极低静态电流的效电路,因为输出必须提供反馈电流。在该实施过程中,输出必须根据增益后的电压失调 VOS调整(并非易事),或者需要断开以上原理图中的 50Ω 电阻器,以消除反馈电流。双放大器环路可通过增加另一个放大器来达到零输出要求。精心选择低输入偏置电流环路放大器,可使输出电流产生的误差非常小。

此外,三运算放大器环路也可帮您测量IQ,但要注意被测量器件输出端的1MΩ电阻器,这将成为一个问题,因为无论测量哪种参数,它总是一个寄生负载。如果测 量输出负载电流,该电阻器就代表一个附加负载。此外,还必须考虑该电阻器的噪声问题,在0.1Hz至10kHz的频率下1MΩ电阻器的噪声为85μVp- p。使用100kΩ电阻器可将噪声降低至27μVp-p。因此,降低电阻器值可降低噪声,但被测量器件输出端的寄生电阻器负载随后会更明显。

电压失调

VOS测试是测量运算放大器大多数其它DC技术参数的基础。因此要格外注意测试电路,以确保在测试其它参数时电路也能良好工作。如果没有选择好该测试配置,会影响到其它DC测量。

VOS 的定义方式有多种,常见方式包括:“无输入信号或无电源电阻时提供零输出电压所需的差分DC输入电压”(参考资料2),或者“在任一输入端至接地的路径中 无其它输入信号及电阻为零时提供零输出电压所需的差分DC输入电压”(参考资料3)。另一种定义方式为“在输入偏置电流为零时在运算放大器输出端提供零电 压所需的差分DC输入电压”,这是测量输入失调电压的理想理论方法,并不具有实践意义,因为零输入偏置电流的运算放大器并不存在。

根据以上定义,您既可将低输出、高精度、高分辨率的可变电压电源连接至运算放大器的输入端,也可调节输入电压,直到输出电压为零。那么输入失调电压就只是所应用输入电压的反选。

这种方法存在两个严重问题。在测试具有极高开环增益的运算放大器时,必须确保电压电源的分辨率小于1微伏才能保证获得任意程度的可重复性。此外,还必须使用 迭代接近法使输出电压为零。系统中的噪声会耦合到电压电源和运算放大器中,使高速自动化测试环境下的测量和控制几乎无法实现。

图2 使用该电路测量电压失调 VOS

由于理想方法的这些问题,因此在工作台测试环境下所选择的常用方法是将被测试器件放在反相增益配置中,如图2所示。这种方法的优势在于不仅被测试器件很稳定,而且通常不需要额外的补偿。

此外,测试电路可能还需要在非反相输入与接地之间提供一个50Ω电阻器,以抵消输入偏置电流。不过,对于输入偏置电流极低的运算放大器而言,该电阻器的 真正“贡献”就是增加噪声。对于100pA的器件来说,没有该电阻器时附加误差只有0.005μV。这种抵消作用只有在偏置电流的方向和量级都相等时才起 作用。

图2中的电路是图1中自测试求和点方法的简略,但没有电阻器R1和R2。该电路对大多数运算放大器来说具备固有的稳定性,其通常可压倒任何潜在的不足,使之成为测试电路。

如果使用图2中的测试电路进行其它测试,其缺点就会显现。例如,图2中的电路会对测量IQ和AOL等其它参数产生影响。

这种未驱动的电路会导致VOS误差,误差值等于(VOS* 闭环增益)* AOL(单位是V/V)。该误差可能无关紧要,也可通过应用适当的VIN使VOUT为0.0V来降低。

可使用以下计算公式 1 调整所需输出的输出端误差补偿公式。

公式1:

VOUT= (2 * ASJ+ ACL- ASJ) * VOUT(理想)

其中ASJ是求和点增益,ACL是闭环增益。

通常可在测试环路中使用一个附加放大器,如图1双放大器环路所示。这种配置接近VOS定义的要求。被测试器件的输出保持在环路放大器至接地的VOS之内。 如果环路放大器支持VOS调节,或者您可通过控制非反相输入来消除失调,就可以不管环路放大器的失调。通过这种方法,您就可使被测试器件的输出为零。在 VOUT端测得的电压为1001*VOS。除非有负载连接至被测试器件的输出端,否则该输出必须只提供环路放大器输入偏置电流。在测量静态电流时,这对于 低IQ部件而言是个重要的注意事项。在前面的两款电路中,被测试器件必须将反馈电流提供给Rf。

通过将环路放大器的非反相输入连接至可编程电压电源,便可测量运算放大器的其它性能参数,例如AOL、输出摆幅和CMRR。由于环路控制电压是变化的,因此被测试器件的输出会尝试与控制电压匹配。

注意,双放大器环路有以下缺点:

比自测试电路更复杂; 需要环路补偿,因为电路本身并不稳定; 只能在环路放大器的共模范围内控制被测试器件的输出。

如果环路未得到适当补偿,电路就会振荡。您可通过与Rf并联一个适当的电容器来稳定环路。为环路放大器布置适当的RC组合也能稳定环路。我们将在以后的文章中探讨该环路补偿问题。

双放大器环路测试法的一种变化形式为三放大器环路,其可通过电流引导实现对被测试器件输出电压的控制。该环路的补偿可通过第二个环路放大器的RC组合进行设 置。与在双运算放大器电路中一样,被测试器件的电压失调也是在VOUT端测量,而且VOUT是电压失调的1001倍。该电路拓扑可解决前一种电路的被测试 器件输出摆幅限制问题。如果需要更大的输出摆幅,可以减小与环路控制电压串联的电阻器。

注意,三放大器环路存在如下缺点:

比其它电路更复杂; 需要环路补偿,因为电路本身不稳定; 被测试器件的输出总是具有1MΩ的负载。

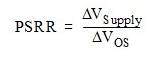

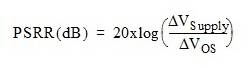

电源抑制比

PSRR是电源电压变化与运算放大器输入失调电压变化的比值。简单来说,就是运算放大器在特定范围内抑制电源电压变化的能力。由于需要失调电压来完成该测 量,因此您可使用现有技术来测量VOS。图1中的三种测试环路都可用来完成PSRR测量。方法是将电源+VS和-VS设置为被测试器件的电源电压,并 测量1001*VOS。接下来,将电源电压设置为被测试器件的电压,然后再次测量1001*VOS。公式2和公式3是PSRR的计算方法。

公式2:

公式3:

在使用这种方法时,有些运算放大器需要考虑其它因素。这些运算放大器有足够低的工作电压,电源的中间点(零共模电压)可超过低电源配置运算放大器所允许的 大共模电压。有些轨至轨输入器件有多个输入级,可在这种条件下平稳工作,但它们会转换至不同的输入级,导致PSRR计算误差。在这两种放大器中,固定共模 电压可防止共模饱和或输入级转换。为PSRR测试的这两种测量方法保持恒定共模电压,会产生一个可在PSRR计算过程中抵消的错误。这些器件所需的实际共 模电压将根据放大器输入级的拓扑变化而变化。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

SiC 和 GaN 功率器件的可靠性和质量要求

比对隔离电源与非隔离电源

基于形式的高效 RISC-V 处理器验证方法

TI 利用两种控制方案降低 BLDC 电机驱动器的噪音

高速数字接口测试,让容限测试更高效