知存科技王绍迪:2023年推出第三代存内计算芯片

当前,硅基芯片已经接近物理材料极限,而以人工智能、大数据、超级计算机等对大算力提出越来越高的要求,使得单纯靠缩微化制程已经无法满足需求,而且成本急速攀升,亟需一种新的芯片技术来解决算力滞后的问题。

最近几年,存算一体芯片成为资本和市场热捧的火热赛道,被认为是破解芯片缩微化难题的主要解决技术路线之一。在2022国际集成电路展览会暨研讨会(IIC2022)全球CEO峰会上,知存科技创始人兼CEO王绍迪以“WTM存内计算芯片应用及发展”为主题,详细介绍了最新存内芯片WTM2101产品优势以及相关应用场景,同时对知存科技未来发展规划作了相关分享。

知存科技创始人兼CEO王绍迪

如何破解存储墙、能耗墙?

存算一体技术是什么?王绍迪介绍,存算一体技术是最近几年非常火热的一个话题,尤其最近几年相关技术性突破已经吸引了越来越多的注意力及资源投入到相关的技术研发中。“一直以来,知存科技一直专注于存算一体技术的研发。基于数模混合存算一体的技术,也被认为是存算一体中最高效的一项技术,可以去突破存储墙、能耗墙,打破限制的一项技术。”

据悉,知存科技于2017年成立,一直致力于推动存算一体的产业化,但实际上公司核心团队在存算一体技术上已经技术耕耘与沉淀了十年的时间。公司核心团队在2012年设计出第一个芯片,2013年首席科学家就已经进行了存算一体芯片的投片,当时大部分人甚至还没有听过存算一体技术,也不知道存内计算是什么样的技术。在过去十年存内计算研发历程中,公司创始团队及公司做了很多0到1突破性的研发工作,包括2016年公司首席科学家发表了首个存内计算深度学习芯片。2019年11月,知存科技发布了国际首个存算一体芯片产品WTM1001。

王绍迪表示,“存内计算的计算原理和逻辑计算完全不一样。存内计算的计算原理可以理解成是用存储器做计算,其计算单元不再是逻辑器件、CPU、GPU或者NPU,与这些架构是完全不一样的。存内计算直接运算单元是存储单元本身。我们去做存内计算,就是要解决存储墙、能耗墙得问题。”

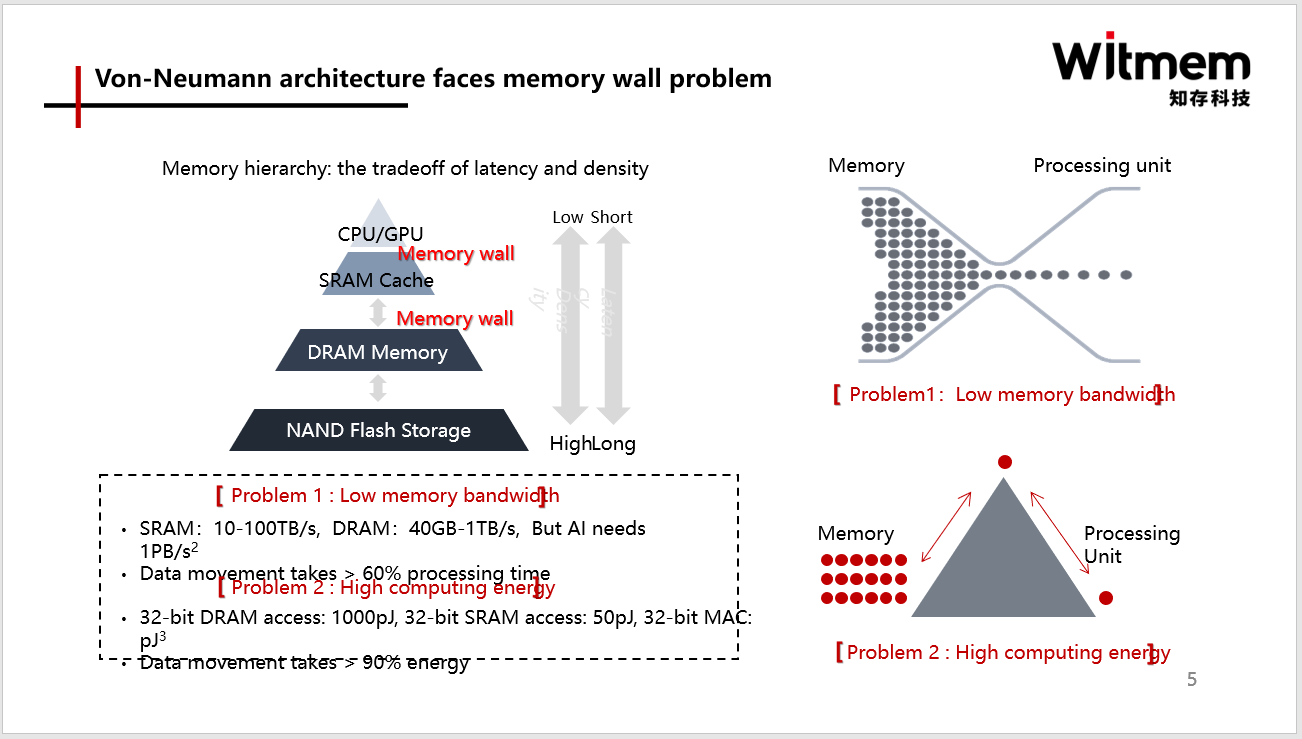

随着人工智能应用得快速发展,以及算法模型的种类参数规模的不断提升,对硬件算力需求也越来越高,导致摩尔定律的演进难以为继。在当前算力急剧增大的时间点,存储墙、能耗墙成为整个芯片计算的瓶颈。

“目前整个计算架构有CPU、GPU、内存、缓存及存储,离计算单元越近的单元,其存储单元速度越快,但是容量越小,离计算单元越远的单元,它的速度慢,但是容量越大。在AI计算时代,数据量是爆炸式增长,我们没法用离计算单元很近的缓存就把所有计算数据存储下来。因此,计算单元中必然会出现数据大量在存储器和计算单元之间搬运。”王绍迪介绍,未来,摩尔定律将走到尽头。从现有芯片架构来看,超过60%时间是花在数据搬运上,超过90%的功耗也损失在数据搬运上。因此,在现有的芯片架构中,大算力芯片最大的瓶颈是数据搬运或者存储墙的问题,并且短时间内看不到一个很好的解决方案。这也是为什么过去几年存内计算或者存算一体技术越来越被关注的原因。

他也介绍,“存内计算技术是利用存储器单元本身模拟或者物理性质完成计算,把原先存储器存储单元变成计算单元。存储器里面存储单元数量是非常多的,如果把每个存储单元都变成一个计算单元,包括它的计算并行度还有计算器件单元,会比现在的NPU、GPU量级高出两到三个的数量级。因此,存算一体技术具有巨大的发展潜力。”

另外,存算一体技术利用了存储器的结构,非常适合人工智能或者一些数据处理矩阵类的计算。因为这些矩阵类计算在传统架构当中对存储器读取次数可能要几万次、几十万次。但在存算一体架构中,利用存储器一次读取操作,就可以完成整个矩阵的计算,相当于原先要做几万次存储器读写操作,在存算一体芯片中只需要一次。那么,存算一体技术就可以大幅度减小计算单元调用次数,减少存储器次数,提高运算的效率。

不过,王绍迪也指出,存算一体技术具有很多架构上的优势,但其技术挑战难点也很多。在存算一体芯片中,计算单元不再是逻辑计算单元,没法用现有芯片设计的工具或者芯片设计的方法去设计,必须采用新的一种基于模拟电路的设计,而且其中还有很多“技术无人区”需要探索。

WTM2101芯片的优势及相关应用

过去十年,知存科技核心团队不断迭代芯片技术接近20次,也进行了5年重点技术研发,使其始终处于行业领先地位。2021年2月,知存科技完成WTM2101芯片小批量试产投片,今年实现WTM2101芯片量产投产,其也是国际首个量产的存内计算SOC芯片。

那么,WTM2101芯片主要优点是什么?王绍迪作了一个对比:在比市场上算法算力大出10倍以上的算法放在存算一体芯片中运行,可以看到其可以完全满足计算需求,且只有现有最佳解决方案20%-40%的功耗。因此,相当于在功耗降低情况下又可以把算力提升10倍以上,整体能效提升可以达到50倍以上,并且芯片采用WLCSP的封装仅有非常小的体积。WTM2101芯片是一个适合于用在低功耗包括电子设备、可穿戴设备等应用的芯片,而且它的算力也是非常高。

王绍迪介绍,WTM2101芯片采用存内计算芯片架构,有1.8兆赫存内计算的单元,采用最常用的存储介质Flash。在SOC芯片里,Flash单元提供50Gops算力,不由任何计算单元提供,因而其算力非常大。同时,这个芯片里也采用一个Risc-V的CPU,大概是148MHz,但是它的算力也跟正常嵌入式CPU算力是相当的。这个芯片在运行AI计算中有非常强大的算力,有50Gops的算力。此外,该款芯片还提供常规算法运用所需要的,包括需要运行的RAM和常规通用的接口,不过但是它的运行功耗很低,运行功耗1毫安以内就可以实现复杂的算法。

目前,该款芯片主要应用在智能语音、智能手表等应用,未来也将应用于更多的应场景中,比如语音指令、声音增强、健康检测、降噪处理、手势识别、视觉识别、低功耗/高精度定位计算等。

其中,这款芯片主要应用于语音增强,可以通过深度学习的算法把人声和噪声分离开,其具有足够高的算力,比一般市场上穿戴设备跑的算力高出4-8倍的级别,但是它的功耗却还降低了1倍。同时,这个芯片可以进行命令词的识别,最多可以做到300个词连续识别,识别率可以达到95%,误识别率在24小时一次以内,并且功耗非常低,且响应速度也非常好。

?在穿戴领域中,该芯片适合做健康监控,包括PPG、ECG、G-sensors的数据,通过融合的算法提取出来,得到更精准的心律、血压等数据,适合在运动情况下区分信号是来自于真正的心律的还是血氧的信号,还是来自运动的干扰。王绍迪表示,目前基于深度学习的健康检测算法,已经在高端运动设备中得到应用,但一般功耗都比较高,而这款芯片可以把这个功耗降到4-8倍的级别,是一个非常低功耗的运行算法。

目前来看,知存科技现有存内计算的产品,主要针对低功耗、小型化设备、穿戴设备、电子设备应用产品,主要应用场景限制在低功耗的场景。但王绍迪表示,目前数据处理、人工智能计算已经进行到二维、三维的计算,意味着需要进行立体的数据处理,这非常适合存算一体的芯片架构。

在接受电子工程专辑采访中,他也表示,存算一体技术最大的挑战就是来自生态的建立,“过去几年,存内计算技术发展非常快,但存算一体计算范式跟现在的算法不一样,其在存算一体中训练出来,且在数模混合结构中训练,最大的问题在于怎么把现在应用的算法更好地在这种新的计算方式中实现,因此需要一个生态的建立。”

对此,知存科技也作了相关的规划:一是针对存算一体开发如何训练算法,且更好适合存算一体的芯片;二是把存内计算的运算模式,即在存储器当中,基于存储器的物理性质,以存储单元进行计算,把这种物理的性质带到算法的训练过程当中,以在训练过程中了解到运算的特点,训练出来的算法更适合于存内计算;三是做一个预测性的工作,比如在芯片中到底跑出多快的速度、什么样的功耗、精确度,不同环境下可以做到什么水平,即以一个很准确的预测模型做到效果的提前预测,帮助用户开发存内计算产品。

第三代存内计算产品“呼之欲出”

经过过去几年的技术研发沉淀,包括知存科技在内的企业的存算一体技术发展非常快,也陆续推出了相应的产品。王绍迪预计,存内计算每年算力将会提高10倍以上,“毕竟现在存内计算发展还处于‘婴儿阶段’,现在采用的存储器容量都是在几兆级别。目前已经非常成熟的存储器已经达到TB级别,像存内计算兆B级别到TB级别,还有百万倍提升空间。未来随着存储器容量越来越大,算力也会越来越大。”

他还透露,2023年知存科技将会推出第三代存内计算架构产品——WTM-8和WTM-C?series,最高可以支持100Tops左右的算力,同时也会推出10-30Tops不同档次算力的存内计算产品,精度也从现在的8比特上升到16比特精度,运算效率从现在10GTOPS/W达到40GTOPS/W的运行效率,主要针对4K、8K更高分辨率的成象和显示处理。他表示,“目前第三代芯片已经完成验证,预计明年会完成量产。第三代存内计算架构是一个更持久的、适用于可拓展的架构,不再是每一代芯片每一年都换一个架构,未来几年可以持续用第三代存内计算架构解决算力的问题。”

在一些底层的工艺上,知存科技作为创新型的研发企业,不只做芯片的设计工作,从2021年开始就与代工厂深度合作,进行诸多工艺改良。据透露,预计2023年底知存科技将推出一个更适用于存内计算存储单元的结构,单个单元可以存储多4倍的数据。

同时,知存科技还在做异构多层的工艺,使单个存内计算阵列容量会做得更大。如同芯片在单位面积下集成的晶体管越多,计算性能就越强。而知存科技也在存内计算芯片中研发在单位面积下集成更多的计算单元,以大幅度提升运算效率、能效、成本。

另外,王绍迪也介绍,知存科技也在积极探索先进的集成封装工艺,包括chiplets。他认为,chiplets非常适合存内计算跟不同其他计算单元融合,因为存内计算主要单元介质是存储器。未来,随着chiplets的发展,存内计算芯片架构在集成CPU、GPU以及其他逻辑单元上会更加容易。

他也指出,现在先进的3D集成工艺,也可以让存储单元更好跟先进工艺集成。鉴于存储器工艺与逻辑工艺之间的代差,先进的3D集成工艺可以让存内计算跨过代差,更好利用先进工艺发挥其优势。目前知存科技已经完成很多研发、专利布局。

在接受电子工程专辑采访被问及“对于2023年苹果将推出MR头显设备”的看法时,王绍迪也表示很期待。他认为,未来元宇宙产品的交互方式值得关注,而存内计算芯片未来将发挥重要作用。

责编:Jimmy.zhang